Programa de Doctorado en Ingeniería Mecatrónica

Departamento de Arquitectura de Computadores

Escuela de Ingenierías Industriales

## TESIS DOCTORAL

## Accelerating Time Series Analysis via Near-Data-Processing Approaches

Iván Fernández Vega

Abril de 2023

Dirigida por: Óscar Plata, Eladio Gutiérrez

EDITA: Publicaciones y Divulgación Científica. Universidad de Málaga

Esta obra está bajo una licencia de Creative Commons Reconocimiento-NoComercial-SinObraDerivada 4.0 Internacional:

https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode

Cualquier parte de esta obra se puede reproducir sin autorización

pero con el reconocimiento y atribución de los autores.

No se puede hacer uso comercial de la obra y no se puede alterar, transformar o hacer obras derivadas.

Esta Tesis Doctoral está depositada en el Repositorio Institucional de la Universidad de Málaga (RIUMA): riuma.uma.es

#### DECLARACIÓN DE AUTORÍA Y ORIGINALIDAD DE LA TESIS PRESENTADA PARA OBTENER EL TÍTULO DE DOCTOR

#### D. Iván Fernández Vega

Estudiante del programa de doctorado Ingeniería Mecatrónica de la Universidad de Málaga, autor de la tesis, presentada para la obtención del título de doctor por la Universidad de Málaga, titulada: Accelerating Time Series Analysis via Near-Data-Processing Approaches

Realizada bajo la tutorización de Óscar G. Plata González y dirección de Óscar G. Plata González y Eladio D. Gutiérrez Carrasco.

#### DECLARO QUE:

La tesis presentada es una obra original que no infringe los derechos de propiedad intelectual ni los derechos de propiedad industrial u otros, conforme al ordenamiento jurídico vigente (Real Decreto Legislativo 1/1996, de 12 de abril, por el que se aprueba el texto refundido de la Ley de Propiedad Intelectual, regularizando, aclarando y armonizando las disposiciones legales vigentes sobre la materia), modificado por la Ley 2/2019, de 1 de marzo.

Igualmente asumo, ante la Universidad de Málaga y ante cualquier otra instancia, la responsabilidad que pudiera derivarse en caso de plagio de contenidos en la tesis presentada, conforme al ordenamiento jurídico vigente.

En Málaga, a 24 de abril de 2023

| Fdo.: Iván Fernández Vega<br>Doctorando              | Fdo.: Óscar G. Plata González<br>Tutor                   |

|------------------------------------------------------|----------------------------------------------------------|

| Fdo.: Óscar G. Plata González<br>Directores de tesis | Fdo.: Eladio D. Gutiérrez Carrasco                       |

| E EFOM AENOR                                         | Edificio Pabellón de Gobierno. Campus El Ejido.<br>29071 |

beaua

29071 Tel.: 952 13 10 28 / 952 13 14 61 / 952 13 71 10 E-mail: doctorado@uma.es

## CERTIFICADO AUTORÍA DIRECTORES

Dr. D. Óscar G. Plata González. Catedrático del Departamento de Arquitectura de Computadores de la Universidad de Málaga. Dr. D. Eladio D. Gutiérrez Carrasco. Profesor Titular del Departamento de Arquitectura de Computadores de la Universidad de Málaga.

#### **CERTIFICAN:**

Que la memoria titulada "Accelerating Time Series Analysis via Near-Data-Processing Approaches", ha sido realizada por D. Iván Fernández Vega bajo nuestra dirección en el Departamento de Arquitectura de Computadores de la Universidad de Málaga y constituye la Tesis que presenta para optar al grado de Doctor en Ingeniería Mecatrónica.

En Málaga, a 24 de abril de 2023

Dr. D. Óscar G. Plata González. Codirector de la tesis. Dr. D. Eladio D. Gutiérrez Carrasco. Codirector de la tesis.

### AUTORIZACIÓN LECTURA DE LA TESIS

Los abajo firmantes declaran, bajo su responsabilidad, que autorizan la lectura de la tesis del doctorando D. Iván Fernández Vega, con DNI , titulada "Accelerating Time Series Analysis via Near-Data-Processing Approaches".

En Málaga, a 24 de abril de 2023

Dr. D. Óscar G. Plata González. Codirector de la tesis. Dr. D. Eladio D. Gutiérrez Carrasco. Codirector de la tesis.

#### INFORME DE UTILIZACIÓN DE PUBLICACIONES QUE AVALAN LA TESIS DOCTORAL

Dr. D. Óscar G. Plata González y Dr. D. Eladio D. Gutiérrez Carrasco, codirectores de la tesis doctoral de D. Iván Fernández Vega, con DNI , titulada "Accelerating Time Series Analysis via Near-Data-Processing Approaches", declaran que ninguna de las publicaciones que avalan dicha tesis han sido utilizadas en tesis doctorales anteriores.

En Málaga, a 24 de abril de 2023

Dr. D. Óscar G. Plata González. Codirector de la tesis.

Dr. D. Eladio D. Gutiérrez Carrasco. Codirector de la tesis.

A mi hermano Antonio

## Agradecimientos

Sirvan estas líneas para agradecer a todas aquellas personas y entidades que de alguna manera han contribuido a que esta tesis haya sido posible.

En primer lugar, agradezco a mis directores de tesis, Óscar Plata y Eladio Gutiérrez por darme la posibilidad de realizar esta tesis con ellos y unirme a su grupo de investigación, Aldebarán. Este entorno ha servido para motivarme y aspirar a generar resultados de calidad. Gracias por ayudarme a mejorar mi autonomía en la generación de ideas y al mismo tiempo proveerme del feedback y directrices necesarias para tomar el camino más exitoso desde el punto de vista académico. Ha sido un verdadero placer compartir estos años con vosotros.

En segundo lugar, me gustaría agradecer a mis compañeros por haber contribuído a crear un ambiente ameno durante estos años. Especial mención merece Ricardo, ha sido muy enriquecedor compartir grupo de investigación y tu feedback ha sido muy valioso. Por otro lado, José Carlos, Andrés, Rubén, Bernabé, Fran, José Manuel, Denisa y Elena: los ratos que hemos pasado juntos y las discusiones que hemos tenido sin duda han contribuido a generar nuevas ideas y solventar los desafíos que han ido aconteciendo. No me olvido de los técnicos, Paco y Juanjo, ni de Carmen, cuyo suporte ha sido vital durante estos años.

Third, I would also like to really thank Prof. Onur Mutlu and from SAFARI research group at ETH Zürich for giving me the opportunity of joining his group. I find myself very fortunate of being part of this top-class environment. My two stays there were extremely productive not only from the academic point of view but also from a personal grow perspective. I really like that this collaboration is still going on and hope to continue contributing to the group. I would also like to thank Prof. Juan Gómez-Luna for mentoring me there over these years at SAFARI, and both Christina Giannoula and Aditya Manglik, who more than collaborators I consider as very good friends. I hope we continue collaborating in the future with you in exciting and top-notch projects!

En cuarto lugar, me gustaría agradecer a mis padres, Antonio y Victoria, el apoyo prestado durante estos años, el haberme inculcado el valor de las cosas y el hacerme ver que la perseverancia son claves para conseguir los objetivos que me propongo. Aunque mi hermano Antonio no pueda entender estas palabras, también le agradezco a él haber estado ahí y de alguna manera influenciarme positivamente. También agradezco a mi abuelo Cristóbal, por transmitirme el buen hacer, y al resto de mi familia en general. Por último, me gustaría agradecerle a Miriam estar a mi lado y apoyarme durante los episodios más difíciles, tu cariño ha sido clave y muy importante para mi.

Finalmente, también debo agradecer las fuentes de financiación que han contribuído a esta tesis. En concreto, a los proyectos TIN2016-80920-R, PID2019-105396RB-I00, UMA18-FEDERJA-197 y JA P18-FR-3433, y las Eurolab4HPC y HiPEAC collaboration grants.

## Abstract

The explosion of the Internet-Of-Things and Big Data era has resulted in the continuous generation of a very large amount of data, which is increasingly difficult to store and analyze [112]. Small sensors and devices produce a significant portion of this data [200], which includes observations (e.g., temperature, voltage, sound) sampled over time. Such a collection of data is also referred to as a time series, a common data representation in almost every scientific discipline and business application [167], for instance, epidemiology, genomics, neuroscience, environmental sciences, and stock markets. Time series analysis (TSA) is an useful set of tools that split the time series data into *subsequences* of consecutive data points to extract valuable information. This information can be used, for example, to filter out irrelevant subsequences or to find subsequences of interest. In real-world applications, TSA can perform heart beat analysis on a mobile medical device to predict a heart attack [118] or early earthquacke detection [41]).

In this thesis, we characterize state-of-the-art time series analysis algorithms and find their bottlenecks in commodity architectures. Based on those bottlenecks, we propose software and hardware solutions to accelerate time series analysis and make its computation as energy-efficient as possible. To this end, we provide four contributions: PhiTSA, NATSA, MATSA and TraTSA.

First, we present *PhiTSA*. In this work, we optimize a state-of-the-art TSA algorithm in a many-core processor with integrated 3D-stacked RAM (Intel Xeon Phi). Our implementation exploits the underneath hardware as much as possible by adding vectorization and the use of two memory technologies (slower/faster). We use this implementation to identify the hotspots of the application, and we find that 1) the arithmetic intensity of the algorithm is very low and 2) when using the (faster) 3D-stacked memory, the performance increases significantly. Based on that, we conclude that the algorithm is memory bound.

Second, we present *NATSA*. In this work, we propose a novel Processing-Near-Memory accelerator based on 3D-stacked RAM that aims to reduce the memory

boundeness of TSA. The key idea is to place custom floating-point compute units close to the memory stack, improving the bandwidth and reducing latency. By reducing the generality of a CPU, NATSA provides the highest performance and best energy-efficiency when compared to its baselines.

Third, we propose *MATSA*. In this work, we propose a Processing-Using-Memory accelerator based on non-volatile memory cells that minimizes data movement by performing in-situ computation. The key idea is to use the actual memory cells in conjunction with reconfigurable sense amplifiers to perform the TSA computation. MATSA provides the highest performance end energy efficient solution so far for a wide range of time series applications.

Finally, we present *TraTSA*. In this work, we study the TSA algorithms from the software point of view, and find that floating-point operations are a big contributor to the energy consumption. Based on that, we evaluate the potentials of TSA when using a transprecision computing approach. Transprecision computing enables the possibility of reducing the number of bits of the floating-point operations while obtaining accurate results. To this end, we propose a transprecision framework that demonstrates that TSA algorithms are good candidates for reduced-precision computation.

# Contents

| Agrade  | ecimientos                              | I    |  |

|---------|-----------------------------------------|------|--|

| Abstra  | act                                     | III  |  |

| Conter  | ats                                     | IX   |  |

| List of | Figures                                 | XVI  |  |

| List of | Tables                                  | XVII |  |

| 1 In    | ntroduction                             | 1    |  |

| 1.1.    | TSA Applications                        | . 3  |  |

| 1.2.    | TSA Bottlenecks                         | . 4  |  |

| 1.3.    | Thesis Motivation and Contributions     | . 8  |  |

| 1.4.    | Thesis Structure                        | . 10 |  |

| 2 B     | ackground and Related Work              | 11   |  |

| 2.1.    | Time Series Analysis                    | . 11 |  |

|         | 2.1.1. SCRIMP Implementation            | . 14 |  |

|         | 2.1.2. SCAMP Implementation             | . 16 |  |

|         | 2.1.3. DTW Implementation               | . 17 |  |

| 2.2.    | Mitigating the Data Movement Bottleneck | . 19 |  |

|         |                                         |      |  |

|      | 2.2.1.  | Processing-Near-Memory                            | 19        |

|------|---------|---------------------------------------------------|-----------|

|      | 2.2.2.  | Processing-Using-Memory                           | 21        |

| 2.3. | Transp  | precision Computing                               | 23        |

| 3 Pł | niTSA:  | Using a Xeon Phi to Optimize and Characterize TSA | <b>27</b> |

| 3.1. | Motiva  | ation and Key Idea                                | 27        |

| 3.2. | Intel 3 | Keon Phi Knights Landing                          | 27        |

| 3.3. | PhiTS   | A Optimizations of SCRIMP                         | 29        |

|      | 3.3.1.  | Updating P and I                                  | 30        |

|      | 3.3.2.  | Increasing Arithmetic Intensity                   | 32        |

|      | 3.3.3.  | Memory Allocation Policy and Scalability          | 34        |

| 3.4. | Evalua  | ation                                             | 35        |

|      | 3.4.1.  | Methodology                                       | 35        |

|      | 3.4.2.  | Results                                           | 35        |

|      |         | Speedups                                          | 35        |

|      |         | Memory Bandwidth Results                          | 38        |

|      |         | Sensibility to Time Series Length and Window Size | 40        |

|      |         | Floating Point Performance                        | 41        |

|      |         | Real-World Applications                           | 41        |

| 4 N  | ATSA    | : A PNM Accelerator for TSA                       | 45        |

| 4.1. | Motiva  | ation and Key Idea                                | 45        |

| 4.2. | NATS    | A Architecture                                    | 46        |

|      | 4.2.1.  | NATSA Processing Units (PUs)                      | 47        |

|      | 4.2.2.  | Workload Partitioning Scheme                      | 48        |

|      | 4.2.3.  | Programming Interface                             | 49        |

| 4.3. | Evalua  | ation                                             | 50        |

|      | 4.3.1.  | Methodology                                       | 50        |

|      | 4.3.2.  | Workload                                          | 52        |

|   |      | 4.3.3. | Results                                                        | 52 |

|---|------|--------|----------------------------------------------------------------|----|

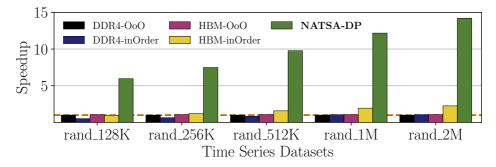

|   |      |        | Performance of NATSA                                           | 53 |

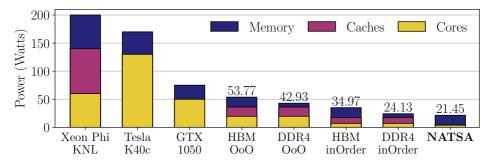

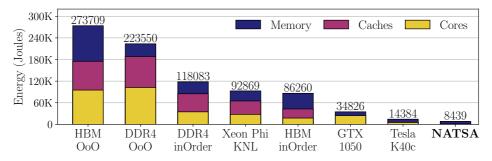

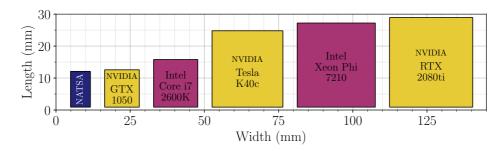

|   |      |        | Power, Energy and Area Consumption                             | 54 |

|   |      |        | NATSA Design Space Exploration                                 | 56 |

|   |      |        | Performance of General-Purpose Cores                           | 56 |

|   |      |        | Accuracy and Sensitivity to Subsequence Length $\ . \ . \ .$ . | 58 |

| 5 | · M  | ATSA   | : A PUM Accelerator for TSA                                    | 59 |

|   | 5.1. | Motiva | ation and Key Idea                                             | 59 |

|   | 5.2. | MATS   | A Architecture                                                 | 60 |

|   |      | 5.2.1. | Overview                                                       | 60 |

|   |      | 5.2.2. | MATSA Subarrays                                                | 61 |

|   |      | 5.2.3. | sDTW Challenges in NVM-PUM                                     | 62 |

|   |      | 5.2.4. | Supported Operations                                           | 63 |

|   |      | 5.2.5. | Data Mapping                                                   | 64 |

|   |      | 5.2.6. | Execution Flow                                                 | 65 |

|   |      | 5.2.7. | System Integration                                             | 66 |

|   | 5.3. | Evalua | tion                                                           | 67 |

|   |      | 5.3.1. | Methodology                                                    | 68 |

|   |      | 5.3.2. | Workloads                                                      | 69 |

|   |      | 5.3.3. | Results                                                        | 70 |

|   |      |        | MATSA Characterization                                         | 70 |

|   |      |        | MATSA Comparison                                               | 72 |

| 6 | · Tr | aTSA   | A Transprecision Framework for TSA                             | 77 |

|   | 6.1. | Motiva | ation and Key Idea                                             | 77 |

|   | 6.2. | TraTS  | A Framework                                                    | 78 |

|   |      | 6.2.1. | Overview of TraTSA                                             | 78 |

|   |      | 6.2.2. | Transprecision SCRIMP-CPU (TranSCRIMP)                         | 80 |

|                               | 6.2.3.                                                                                        | $Transprecision \ SCAMP-CPU \ (\texttt{TransCAMP}) \ . \ . \ . \ . \ . \ 82$ |

|-------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

|                               | 6.2.4.                                                                                        | Transprecision SCAMP-FPGA (TransCAMPfpga) $83$                               |

| 6.3.                          | Top-K                                                                                         | Accuracy Metric                                                              |

| 6.9.                          | Evalua                                                                                        | tion                                                                         |

|                               | 6.9.1.                                                                                        | Methodology                                                                  |

|                               | 6.9.2.                                                                                        | Results                                                                      |

|                               |                                                                                               | Short Time Series Accuracy                                                   |

|                               |                                                                                               | Large Time Series Accuracy                                                   |

|                               |                                                                                               | TraTSA Performance                                                           |

|                               |                                                                                               | Energy Savings                                                               |

| 7 Co                          | onclusi                                                                                       | ons 109<br>Work                                                              |

| 71                            | ruture                                                                                        | WOIK                                                                         |

| 7.1.                          |                                                                                               |                                                                              |

| 7.1.<br><b>Appe</b> r         | ndices                                                                                        | 5 <b>113</b>                                                                 |

| Арреі                         |                                                                                               | n en español 113                                                             |

| Apper<br>A Re                 | esumer                                                                                        |                                                                              |

| Apper<br>A Re                 | esumer<br>Introd                                                                              | n en español 113                                                             |

| Apper<br>A Re                 | esumer<br>Introd<br>A.1.1.                                                                    | <b>n en español 113</b><br>ucción                                            |

| Apper<br>A Re                 | Introd<br>A.1.1.<br>A.1.2.                                                                    | n en español       113         ucción                                        |

| Аррен<br>А Re<br>А.1.         | esumer<br>Introd<br>A.1.1.<br>A.1.2.<br>A.1.3.                                                | n en español       113         ucción                                        |

| Аррен<br>А Re<br>А.1.         | Esumer<br>Introd<br>A.1.1.<br>A.1.2.<br>A.1.3.<br>PhiTS                                       | n en español113ucción                                                        |

| Аррен<br>А Re<br>А.1.         | Esumer<br>Introd<br>A.1.1.<br>A.1.2.<br>A.1.3.<br>PhiTS<br>A.2.1.                             | n en español113ucción                                                        |

| Аррен<br>А Re<br>А.1.         | Esumer<br>Introd<br>A.1.1.<br>A.1.2.<br>A.1.3.<br>PhiTS<br>A.2.1.<br>A.2.2.                   | n en español113ucción                                                        |

| Аррен<br>А Re<br>А.1.<br>А.2. | Esumer<br>Introd<br>A.1.1.<br>A.1.2.<br>A.1.3.<br>PhiTS<br>A.2.1.<br>A.2.2.<br>A.2.3.         | n en español113ucción                                                        |

| Аррен<br>А Re<br>А.1.<br>А.2. | Esumer<br>Introd<br>A.1.1.<br>A.1.2.<br>A.1.3.<br>PhiTS<br>A.2.1.<br>A.2.2.<br>A.2.3.<br>NATS | A en español113ucción                                                        |

| A.3.3. Evaluación                                                    | 123 |

|----------------------------------------------------------------------|-----|

| A.4. MATSA: Un Acelerador PUM para AST                               | 124 |

| A.4.1. Contribuciones                                                | 124 |

| A.4.2. Evaluación                                                    | 124 |

| A.5. TraTSA: Un Framework Transpreciso Para AST $\ .$                | 125 |

| A.5.1. Idea y Motivación $\ldots \ldots \ldots \ldots \ldots \ldots$ | 125 |

| A.5.2. Contribuciones                                                | 125 |

| A.5.3. Evaluación                                                    | 126 |

| A.6. Conclusiones y Trabajo Futuro                                   | 127 |

|                                                                      |     |

| Bibliography                                                         | 131 |

# List of Figures

| 1.1. | Example of TSA application. In this processing flow, TSA acts<br>as a filter to avoid most of the computation by selecting the rele-<br>vant subsequences (anomalies) and discarding the irrelevant ones<br>(expected behavior)                      | 2  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2. | Memory bandwidth usage (bars) and normalized performance (lines) of a parallel and vectorized version of SCRIMP [58] running on an Intel Xeon Phi 7210                                                                                               | 5  |

| 1.3. | Roofline analysis of a parallel and vectorized version of SCRIMP [58] running on an Intel Xeon Phi 7210                                                                                                                                              | 6  |

| 1.4. | Roofline analysis of a parallel version of DTW running on an Intel Xeon Phi 7210                                                                                                                                                                     | 6  |

| 2.1. | Example of two subsequences, $T_{i,m}$ and $T_{j,m}$ , of a given time series $T$ . Distance $d_{i,j}$ is calculated from these subsequences. When calculating the matrix profile $P$ , subsequences in the exclusion zone of $T_{i,m}$ are ignored  | 11 |

| 2.2. | A time series with some anomalies (discords) and its matrix profile (MP). The anomalies appear as higher distance values in the profile.                                                                                                             | 12 |

| 2.3. | Example of distance matrix (D), profile (P), and profile index (I). $P_i$ holds the minimum distance calculated in row $D_i$ , and $I_i$ holds the index $j$ of the subsequence that has such distance. Cells in the exclusion zone are coloured red | 13 |

| 2.4. | Example of similarity calculation between two subsequences (blue and green). The Euclidean approach in a) provides a low similarity as it only compares each $i^{th}$ point of blue with each $i^{th}$ point of green. However, DTW in b) successfully matches the points of the subsequences, thus finds the high similarity. | 14 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

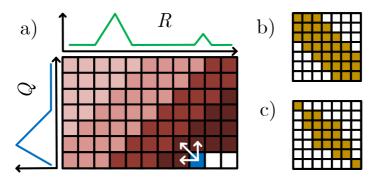

| 2.5. | a) Warping matrix example for a reference time series $R$ and a query subsequence $Q$ . The DTW distance between $R$ and $Q$ is the minimum value of the last row of the matrix. b) Sakoe-Chiba band. c) Itakura parallelogram.                                                                                                | 18 |

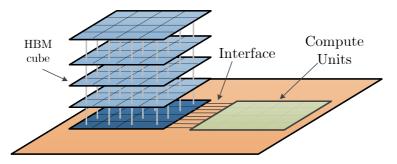

| 2.6. | Sample PNM architecture (I). Compute Units are placed close to the HBM cube, connected via a short and wide interface.                                                                                                                                                                                                         | 20 |

| 2.7. | Sample PNM architecture (II). UPMEM-based PNM system with<br>a host CPU, standard main memory, and PNM-enabled memory<br>(left), and internal components of a UPMEM PNM chip (right).<br>Figure taken from [183]                                                                                                               | 20 |

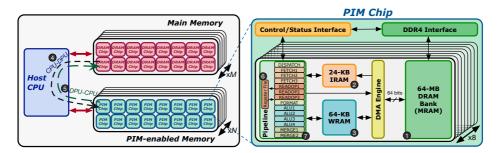

| 2.8. | a) Crossbar organization. b) Magneto-resistive cell. c) Recon-<br>figurable SA that performs in-memory operations based on the<br>voltage across the bitline when two cells are activated                                                                                                                                      | 22 |

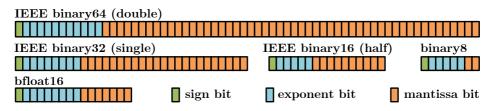

| 2.9. | Overview of the floating-point types used for energy evaluation                                                                                                                                                                                                                                                                | 24 |

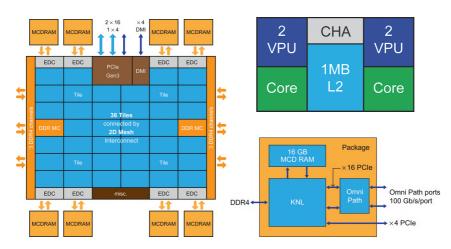

| 3.1. | Intel Xeon Phi KNL overview [93]                                                                                                                                                                                                                                                                                               | 28 |

| 3.2. | Calculation of the Matrix Profile $P$ and the Matrix Profile index $I$ from the distance matrix. For each column (or row) $D_i$ we calculate the minimum distance and the index of the subsequence providing such minimum distance.                                                                                            | 29 |

| 3.3. | SCRIMP's lock-based implementation to update the Matrix Profile<br>and the Matrix Profile index without potential conflicts                                                                                                                                                                                                    | 31 |

| 3.4. | SCRIMP's expanded structure for Matrix Profile distances (top) and indexes (bottom) in the privatization technique.                                                                                                                                                                                                            | 31 |

| 3.5. | Privatization-based implementation of the SCRIMP computation                                                                                                                                                                                                                                                                   | 33 |

| 3.6. | SCRIMP's inner loops unrolling and vectorization                                                                                                                                                                                                                                                                               | 34 |

| 3.7. | SCRIMP speedup in the Intel Xeon Phi KNL, calculated using a random time series of of $2^{17}$ (131072) elements and a fixed window size of 1024.                                                                                                                                                                              | 36 |

| 3.8. | SCRIMP memory bandwidth utilization in the Intel Xeon Phi<br>KNL, using different configurations, normalized as percentage of<br>execution time. DDRo stands for DDR4 ordered and DDRr stands<br>for DDR4 random, while HBMo means HBM+DDR4 ordered and<br>HBMr means HBM+DDR4 random                                                                    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.9. | Average DDR4 bandwidth utilization, measured varying the number of threads in an execution of SCRIMP, using a random series of $2^{18}$ elements and a window of 1024.                                                                                                                                                                                   |

| 3.10 | Average HBM bandwidth utilization, measured varying the number of threads in an execution of SCRIMP, using a random series of $2^{18}$ elements and a window of 1024.                                                                                                                                                                                    |

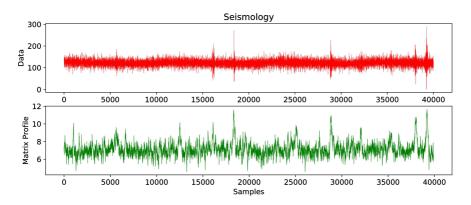

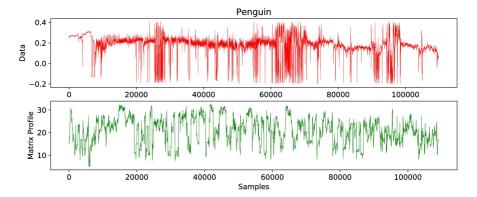

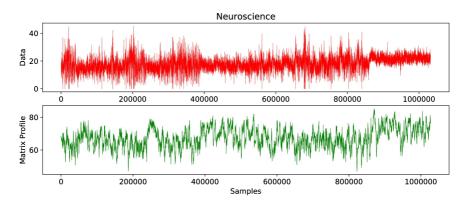

| 3.11 | Seismology data. This dataset, which consists of approximately 40,000 elements, presents several peaks corresponding to earth-<br>quakes. The Matrix Profile is able to accurately identify them, which are represented as higher values of distance for the corre-<br>sponding subsequences, as they are discords with respect to the whole time series |

| 3.12 | Penguin data. This dataset, which consists of approximately 110,000 elements, presents several motifs that can help a biologist to identify when the penguin is diving, for example                                                                                                                                                                      |

| 3.13 | Neuroscience data. This dataset, which consists of approximately 1,030,000 elements, presents several discontinuities which are represented in the graph as values of 0 for readability. The Matrix Profile is able to obtain coherent results even with those discontinuities, proof of robustness of the algorithm.                                    |

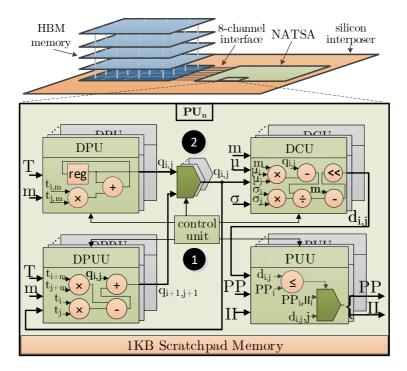

| 4.1. | NATSA design and integration next to HBM memory. NATSA is connected directly to the HBM interface                                                                                                                                                                                                                                                        |

| 4.2. | Example of the diagonal scheduling scheme for two processing units, denoted as $PU0$ (green) and $PU1$ (white). Arrows show direction of computation.                                                                                                                                                                                                    |

| 4.3. | Speedup with respect to the baseline platform (DDR4-OoO) using double precision data.                                                                                                                                                                                                                                                                    |

| 4.4. | Dynamic power consumption for simulated and real hardware plat-<br>forms.                                                                                                                                                                                                                                                                                |

| 4.5. | Energy consumption for simulated and real hardware platforms                                                                                                                                                                                                                                                                                             |

| 4.6.  | Area comparison of different hardware platforms                                                                                                                                                                                                         | 55 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

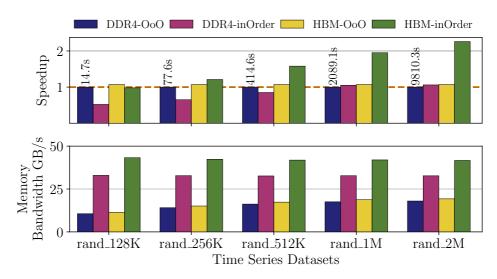

| 4.7.  | Speedup over the baseline DDR4-OoO and memory bandwidth usage for general-purpose platforms                                                                                                                                                             | 57 |

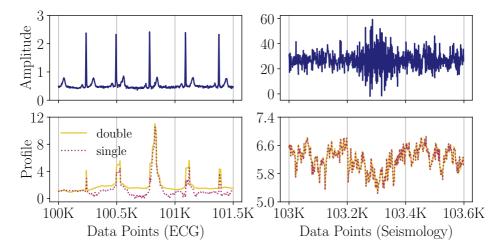

| 4.8.  | ECG (left) and seismology (right) data along with their profiles, using double and single precision, where events are easily visible.                                                                                                                   | 58 |

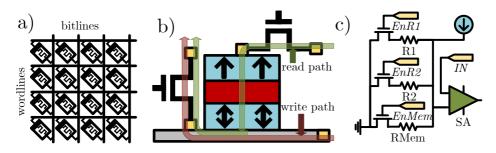

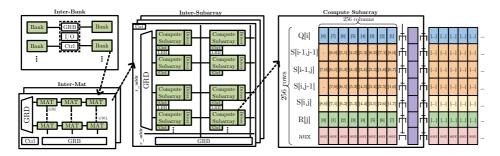

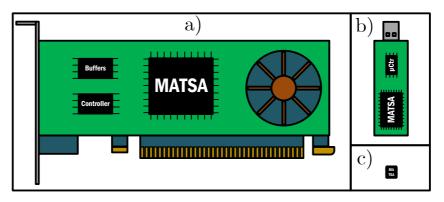

| 5.1.  | MATSA's high-level Architecture and Data Mapping. Note that<br>modifications at <i>Inter-Bank</i> , <i>Inter-Mat</i> , and <i>Inter-Subarray</i> lev-<br>els with respect to common NVM devices are negligible, easing<br>fabrication and compatibility | 60 |

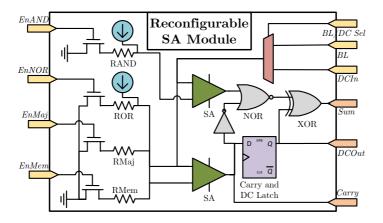

| 5.2.  | MATSA's Reconfigurable Sense Amplifier. Latch register is reused<br>for Addition and Diagonal Copy operations                                                                                                                                           | 62 |

| 5.3.  | Wavefront-based sDTW computation. In a, PEs are able to cal-<br>culate their matrix elements in parallel. In b, the pipeline is full<br>and PEs are also working on different queries                                                                   | 66 |

| 5.4.  | MATSA integration. a) High-performance accelerator (PCIe card). b) Portable accelerator (USB stick). c) Embedded accelerator (small chip).                                                                                                              | 67 |

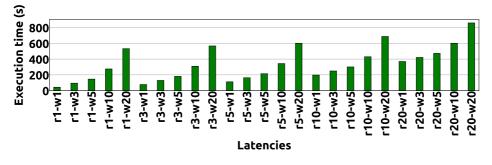

| 5.5.  | Execution time when varying cell read and write la-<br>tencies (ref_size=128K, query_size=8K, num_queries=8K, matsa_cols=128K)                                                                                                                          | 70 |

| 5.6.  | Execution energy when varying cell read and write energies (ref_size=128K, query_size=8K, num_queries=8K, matsa_cols=128K)                                                                                                                              | 71 |

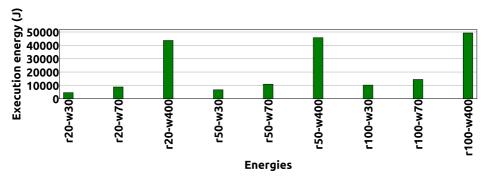

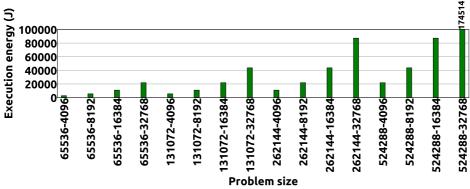

| 5.7.  | Execution time when varying workload sizes (num_queries=8K, matsa_cols=128K)                                                                                                                                                                            | 71 |

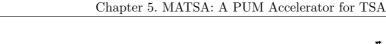

| 5.8.  | Execution energy when varying problem sizes (num_queries=8K, matsa_cols=128K)                                                                                                                                                                           | 72 |

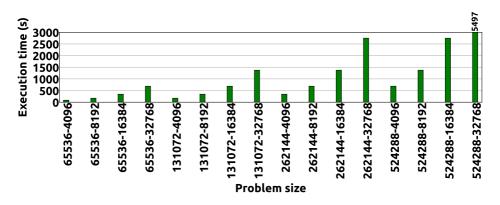

| 5.9.  | Execution time when varying MATSA sizes                                                                                                                                                                                                                 | 72 |

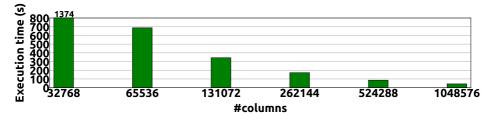

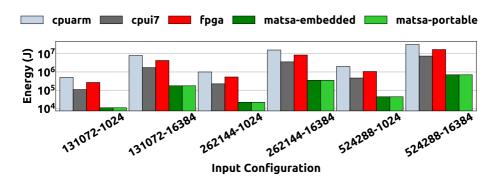

| 5.10. | Execution times of MATSA-Embedded (num_cols=32K) and MATSA-Portable (num_cols=256K) versus baselines for different workload sizes (rd_latency=5ns, wr_latency=10ns)                                                                                     | 73 |

| 5.11. | Execution energy consumption of MATSA-Embedded (num_cols=32K) and MATSA-Portable (num_cols=256K) versus baselines for different workload sizes (rd_energy=50nJ, wr_energy=70nJ)                                                                                                                                                        | 74 |

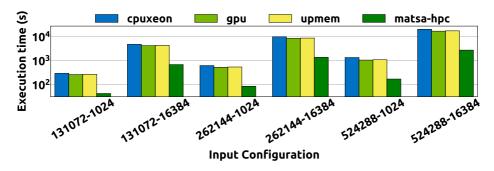

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.12. | Execution times of MATSA-HPC versus baselines for different workload sizes (rd_latency=5ns, wr_latency=10ns, num_cols=1M).                                                                                                                                                                                                             | 74 |

| 5.13. | Execution energy consumption of MATSA-HPC versus baselines<br>for different workload sizes (rd_energy=50nJ, wr_energy=70nJ,<br>num_cols=1M)                                                                                                                                                                                            | 75 |

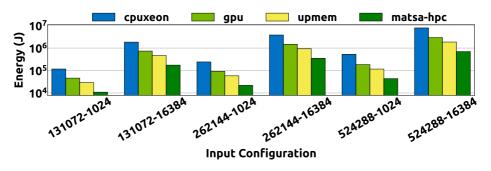

| 6.1.  | TraTSA overview and its components. The user provides a time se-<br>ries file (.txt) and a configuration file (.cfg) to the wrapper. Then,<br>the wrapper invokes matrix profile either in the CPU or in the<br>FPGA. Finally, the wrapper provides the user the transprecision<br>matrix profile (.csv) and some statistics (.stats). | 79 |

| 6.2.  | Example of TraTSA's cfg file                                                                                                                                                                                                                                                                                                           | 79 |

| 6.3.  | Transprecision SCRIMP (TranSCRIMP) algorithm (transprecision operations highlighted).                                                                                                                                                                                                                                                  | 81 |

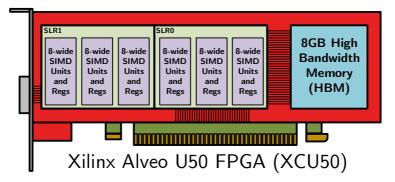

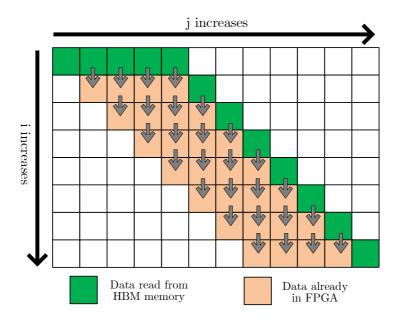

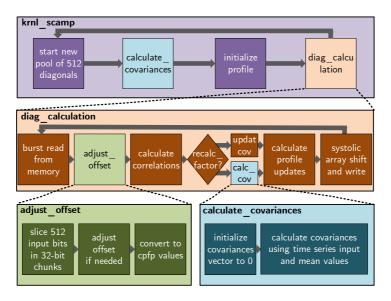

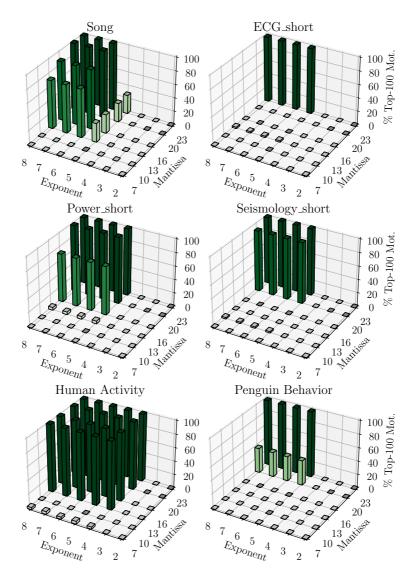

| 6.4.  | FPGA implementation overview. TranSCAMPfpga is composed of six kernels optimized for a Xilinx Alveo U50 FPGA that compute transprecision SCAMP algorithm using the data in the HBM                                                                                                                                                     | 84 |

| 6.5.  | TranSCAMPfpga systolic array example                                                                                                                                                                                                                                                                                                   | 86 |

| 6.6.  | FPGA implementation diagram.                                                                                                                                                                                                                                                                                                           | 86 |

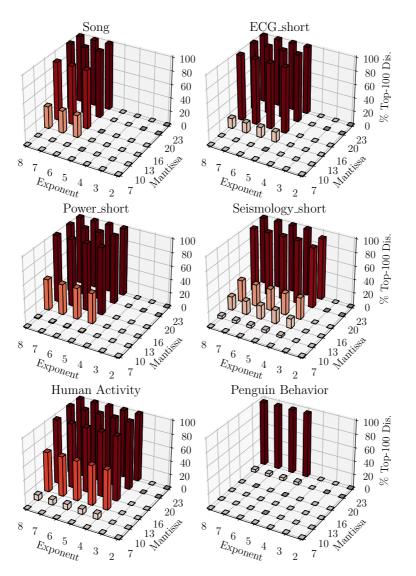

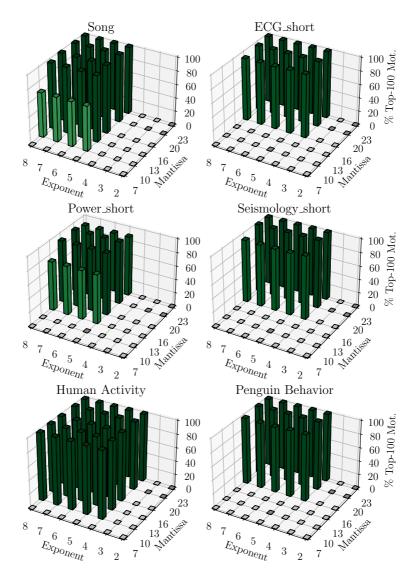

| 6.7.  | <b>TranSCRIMP</b> Top-100 motif accuracy with respect to double                                                                                                                                                                                                                                                                        | 91 |

| 6.8.  | $\ensuremath{\texttt{TranSCRIMP}}$ Top-100 discord accuracy with respect to double                                                                                                                                                                                                                                                     | 92 |

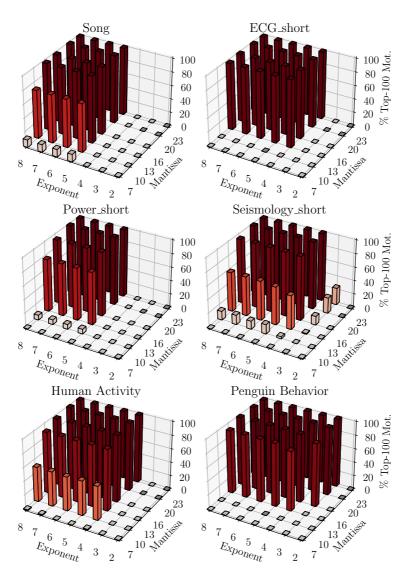

| 6.9.  | <b>TranSCAMP</b> Top-100 motif accuracy with respect to double                                                                                                                                                                                                                                                                         | 93 |

| 6.10. | <b>TranSCAMP</b> Top-100 discord accuracy with respect to double                                                                                                                                                                                                                                                                       | 94 |

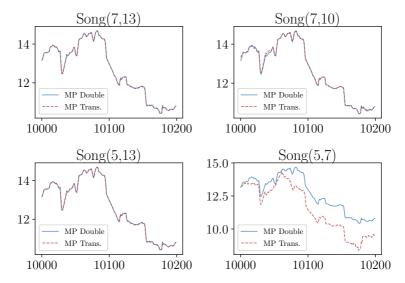

| 6.11. | TranSCAMP Song profile with respect to double. The horizontal axis represents the index of the datapoints within the complete time series and the vertical axis represents the amplitude of the signal.                                                                                                                                | 95 |

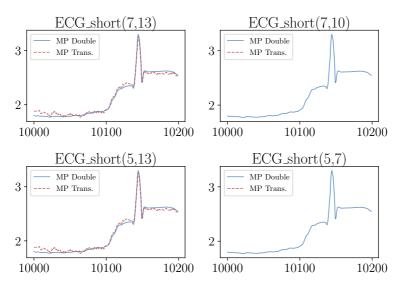

| 6.12. | <b>TranSCAMP</b> <i>ECG_short</i> profile with respect to double. The horizon-<br>tal axis represents the index of the datapoints within the complete<br>time series and the vertical axis represents the amplitude of the<br>signal                                                                                                   | 96 |

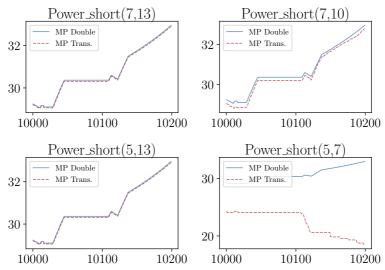

| 6.13. TranSCAMP <i>Power_short</i> profile with respect to double. The horizontal axis represents the index of the datapoints within the complete time series and the vertical axis represents the amplitude of the signal      |

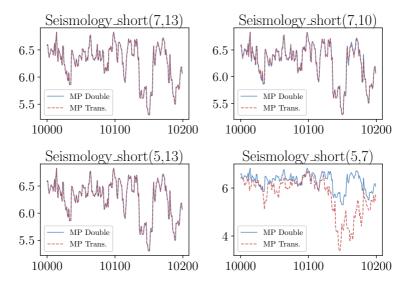

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

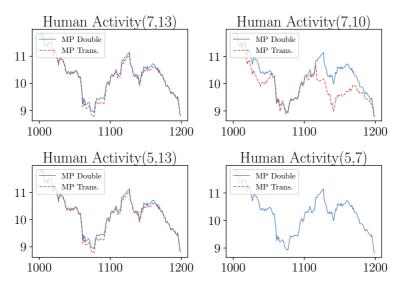

| 6.14. TranSCAMP Seismology_short profile with respect to double. The horizontal axis represents the index of the datapoints within the complete time series and the vertical axis represents the amplitude of the signal        |

| 6.15. TranSCAMP <i>Human Activity</i> profile with respect to double. The horizontal axis represents the index of the datapoints within the complete time series and the vertical axis represents the amplitude of the signal   |

| 6.16. TranSCAMP <i>Penguin Behavior</i> profile with respect to double. The horizontal axis represents the index of the datapoints within the complete time series and the vertical axis represents the amplitude of the signal |

| 6.17. TranSCAMPfpga Top-1000 motif accuracy results with respect to double precision using a recalculation factor of 64K elements 101                                                                                           |

| 6.18. TranSCAMPfpga Top-1000 discord accuracy results with respect to double precision using a recalculation factor of 64K elements 102                                                                                         |

| 6.19. TranSCAMPfpga Top-1000 accuracy results with respect to double precision when varying the recalculation factor                                                                                                            |

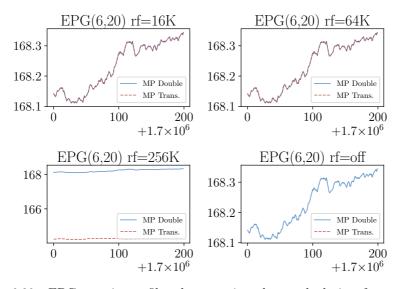

| 6.20. EPG matrix profile when varying the recalculation factor using $\tt TranSCAMPfpga$ for a given mantissa and exponent combination 104                                                                                      |

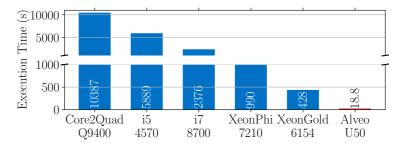

| 6.21. Execution time for different platforms when computing Seismology_short, using a window size of 512 elements (exp. 7 man. 10) 105                                                                                          |

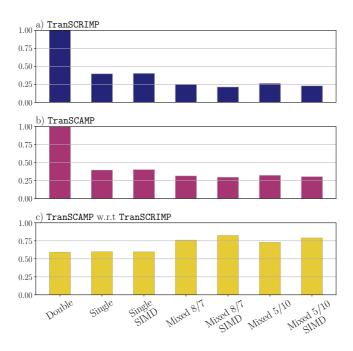

| 6.22. Normalized FPU energy using FPNew                                                                                                                                                                                         |

# List of Tables

| 1.1. | Time Series Analysis application examples                                                                                                 | 3   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1. | Overview of different NVM technologies [45]                                                                                               | 23  |

| 2.2. | Floating-point bit counts, ranges and smallest numbers                                                                                    | 24  |

| 3.1. | SCRIMP execution on Intel Xeon Phi KNL versus STOMP on NVIDIA Tesla $K80^{\ddagger}$ .                                                    | 38  |

| 3.2. | Time for SCRIMP using only DDR4 in random order                                                                                           | 40  |

| 3.3. | Time for SCRIMP using only DDR4 in sequential order                                                                                       | 40  |

| 3.4. | Time for SCRIMP using HBM plus DDR4 in random order                                                                                       | 40  |

| 3.5. | Time for SCRIMP using HBM plus DDR4 in sequential order. $\ . \ .$                                                                        | 40  |

| 3.6. | GFLOP/s for SCRIMP with different configurations                                                                                          | 41  |

| 4.1. | Synthetic time series for performance evaluation                                                                                          | 52  |

| 4.2. | $\ensuremath{\operatorname{Execution}}$ time (in seconds) for single-precision and double-precision.                                      | 54  |

| 4.3. | NATSA design components for 48 PUs                                                                                                        | 56  |

| 5.1. | MATSA design exploration parameters                                                                                                       | 69  |

| 5.2. | Workload parameters used in our evaluation. $\ldots$                                                                                      | 69  |

| 6.1. | TranSCAMPfpga kernel resource utilization                                                                                                 | 87  |

| 6.2. | Time series dataset parameterization                                                                                                      | 90  |

| 6.3. | Mixed precision Top-100 accuracy results                                                                                                  | 99  |

| 6.4. | Energy consumption for different platforms when computing <i>Seis-mology_short</i> , using a window size of 512 elements (exp. 7 man. 10) | 105 |

# 1 Introduction

The explosion of the Internet-Of-Things and Big Data era has resulted in the continuous generation of a very large amount of data, which is increasingly difficult to store and analyze [112]. Small sensors and devices produce a significant portion of this data [200], which includes observations (e.g., temperature, voltage, sound) sampled over time. Such a collection of data is also referred to as a *time series*, a common data representation in almost every scientific discipline and business application [167], for instance, epidemiology, genomics, neuroscience, environmental sciences, and stock markets. *Time series analysis* (TSA) splits the time series into *subsequences* of consecutive data points to extract information.

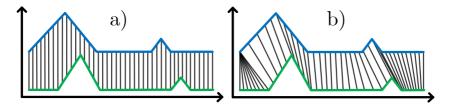

To find subsequences of interest, TSA algorithms define a *distance metric*, e.g., Euclidean Distance (ED) or Dynamic Time Warping (DTW). This distance metric represents how similar are two given subsequences, meaning that the lower the distance value is, the more similar are them. Based on the distance metric, the algorithm classifies the subsequences that have low distance as *motifs* [148] (similarities) and high distance as *discords* [100] (anomalies). This classification is a critical step before further analysis via domain-specific algorithms or human experts, enabling **TSA** as a tool of vital importance and generality.

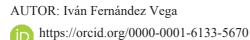

TSA algorithms can be used to filter out those subsequences that match an expected behavior, leaving only anomalies for the computationally expensive domain-specific algorithm (e.g., [126]), i.e., only a small amount of critical data that need to be further analyzed. One example is SquiggleFilter [50], a TSA-based accelerator that processes the Mini-ION sequencer's output and filters everything except sequences of interest, pruning more than 85% of the computation. However, SquiggleFilter optimizations rely on a modified version of DTW that looses generality to other applications. Figure 1.1 describes the filtering process based on an example data flow for electrocardiogram data and a generic TSA algorithm.

Figure 1.1: Example of TSA application. In this processing flow, TSA acts as a filter to avoid most of the computation by selecting the relevant subsequences (anomalies) and discarding the irrelevant ones (expected behavior).

**Key Motivation I:** TSA is useful in many domains, but prior acceleration proposals mostly rely on modifications of the algorithms that loose generality

Diving into the implementation point of view, we find that *Matrix Profile* [196] (MP) is the state-of-the-art set of tools to perform TSA, which comprises of both Euclidean Distance and Dynamic Time Warping algorithms. There are several CPU-based, GPU-based and even FPGA-based MP implementations in the literature [196, 86, 202, 204]. These CPU, GPU and FPGA approaches are embarrassingly parallelizable, relying on simple arithmetic operations over data to calculate distances. In this sense, the naive parallelization approach consists on spreading all the distances to calculate across the computational resources since –in principle– there are no dependencies between them. This scheme provides almost the size of the time series fully independent execution flows, much higher than typical core count in commodity CPUs and GPUs. In order to accelerate parallel implementations of TSA under those architectures, increasing the core count appears to be a promising approach.

With such opportunity in mind, we first characterize a MP implementation in a many-core machine (Intel Xeon Phi KNL) and find that core count is not the only bottleneck for TSA. Concretely, we observe that the scalability stops after a certain number of cores and conclude that *the performance and energy efficiency of TSA algorithms are heavily burdened by data movement*. This observation is based on 1) the low arithmetic intensity of the algorithm and 2) the need to access large amounts of time series data from the memory. In other words, the amount of computation per data access is not enough to hide the memory latency, so the algorithm is memory bound in a conventional CPU architecture. Within this context, Processing-Near-Memory (PNM) and Processing-using-Memory (PUM) place computation closer to data, thus reducing the impact of data movement. Based on this, we consider PNM and PUM architectures as promising approaches to accelerate TSA.

**Key Motivation II:** TSA is bottlenecked in conventional architectures by 1) the low core count with respect to the potential parallelism and 2) data movement between memory and processing units

In the rest of this Introduction chapter, we further elaborate the two key motivation points and present the contributions of this thesis.

#### 1.1. TSA Applications

The first point of motivation of this thesis is based on the fact that TSA constitutes one of the most important data mining primitives thanks to its generality in detecting anomalies and similarities for a wide range of applications. Note that this desirable feature is enabled by the domain-agnostic nature of the TSA algorithms, as their outputs are simple distance values. Table 1.1 presents a few examples of TSA applications.

| Field             | References | Field               | Reference |

|-------------------|------------|---------------------|-----------|

| Bioinformatics    | [51]       | Speech Recognition  | [25]      |

| Robotics          | [175]      | Weather Prediction  | [131]     |

| Neuroscience      | [51]       | Entomology          | [170]     |

| Machine Learning  | [186]      | Geophysics          | [181]     |

| Econometrics      | [83]       | Statistics          | [162]     |

| Finance           | [182]      | Control Engineering | [31]      |

| Signal Processing | [109]      | Pattern Recognition | [189]     |

| Communication     | [111]      | Medicine            | [88]      |

| Astronomy         | [184]      | Social Networks     | [144]     |

| Clustering        | [186]      | Classification      | [99]      |

| Earthquakes       | [181]      | GPS Tracking        | [108]     |

| Virtual Reality   | [169]      | Gesture Recognition | [89]      |

| Trajectories      | [24]       | Traffic Monitoring  | [119]     |

Table 1.1: Time Series Analysis application examples

In statistics, econometrics, meteorology, and geophysics, the primary goal of time series analysis is prediction and forecasting. At the same time, in signal processing, control engineering, and communication engineering, it is used for signal detection and estimation. In data mining, pattern recognition, and machine learning, time series motif and discord discovery are used for clustering, classification, anomaly detection, and forecasting. Finally, the most important application of time series motif and discord discovery is clustering seismic data and discovering earthquake pattern clusters from the continuous seismic recording. Consequently, seismic clustering can be applied to earthquake relocation and volcano monitoring to help improve earthquake and volcanic hazard assessments.

End-to-End Application Benefits of using TSA. TSA is critical for reallife examples of end-to-end applications. For instance, [90] predicts circulatory failure in intensive care units. In this scenario, 90% of the execution time is dominated by TSA preprocessing, while the remainder 10% is used by the machine learning-based application to perform the classification. We also find many other real use case examples that can benefit from this approach, such as:

- Earthquake detection [41]. TSA can process the data from a seismograph and detect anomalies that can be further processed with complex algorithms.

- Electroencephalography [37]. Assuming an electroencephalograph that is monitoring a patient, TSA can be used to detect anomalies and trigger an alarm about that.

- Virus Detection [50]. During the genome assembly process, basecalling is a compute-intensive task that can be skipped for most queries using a TSA-based filter.

Based on that, we conclude that TSA 1) is widely applicable and 2) its acceleration significantly benefits the whole application execution time.

### 1.2. TSA Bottlenecks

The second point of motivation of this thesis is based on the fact that TSA is bottlenecked in commodity architectures. To identify those bottlenecks, we first develop an optimized and vectorized version of a state-of-the-art implementation of Matrix Profile. Then, we characterize it using a many-core machine (Intel Xeon Phi KNL) that also includes High-Bandwidth-Memory (HBM) in

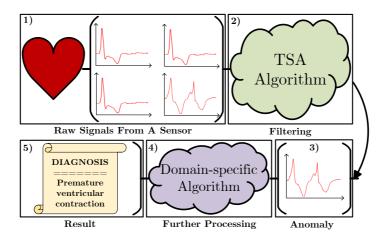

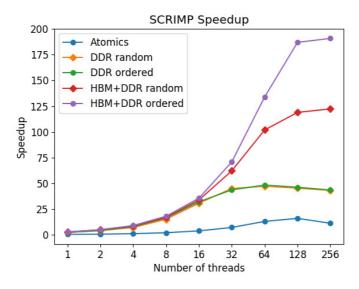

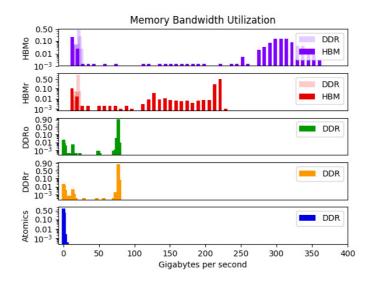

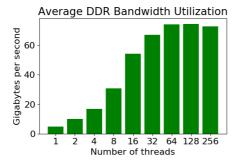

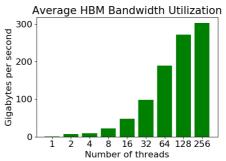

conjunction with conventional DDR4. We first observe that while the hardware thread count (256) of the Intel Xeon Phi is relatively high compared to lower end machines, there are still way more independent executions flows (thousands, millions) than threads. However, thread availability is not the only bottleneck for TSA. In Figure 1.2, we present the performance results normalized to 1 thread (lines) and utilized memory bandwidth (bars) of this Euclidean Distance based implementation of MP, known as SCRIMP. We observe that, when using the DDR4 memory, the performance of SCRIMP does not scale beyond 32 threads, whereas the higher memory bandwidth provided by HBM enables SCRIMP to scale up to 128 threads. This shows that SCRIMP's performance saturates on many-core architectures, because the achievable bandwidth saturates when the number of threads increases.

Figure 1.2: Memory bandwidth usage (bars) and normalized performance (lines) of a parallel and vectorized version of SCRIMP [58] running on an Intel Xeon Phi 7210.

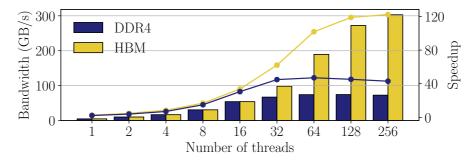

To understand the cause for this memory boundedness, we perform the next experiment. We generate the roofline analysis for SCRIMP, as we show in Fig. 1.3, and observe that the arithmetic intensity of SCRIMP is significantly low. This fact confirms that the memory boundedness of SCRIMP is due to the low arithmetic intensity of the algorithm, which leads processing cores to be underutilized. Based on all these observations, we conclude that the performance of the state-of-the-art CPU-based implementation of SCRIMP is heavily bottlenecked by available memory bandwidth and data movement.

However, based on the similar operational simplicity of the TSA algorithms and the huge amount of data to process, we hypothesize that the bottlenecks are shared across other TSA approaches. To prove this statement, we also characterize a Dynamic-Time-Warping (DTW) implementation in the same architecture as SCRIMP and discuss the bottlenecks in other platforms.

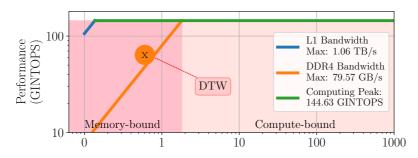

Figure 1.3: Roofline analysis of a parallel and vectorized version of SCRIMP [58] running on an Intel Xeon Phi 7210.

Figure 1.4: Roofline analysis of a parallel version of DTW running on an Intel Xeon Phi 7210.

**CPU platforms**. We profile the performance of DTW using the same manycore processor (Intel Xeon Phi 7210) as we used for SCRIMP, analyzing the execution of 16K queries of 8K elements each that are compared against a reference sequence of 32K elements. Figure 1.4 presents the roofline plot for the experiment.

First, we observe that DTW only exploits 41% of the system's integer peak performance, i.e., 59 GINTOPS out of 145 GINTOPS, and it presents low arithmetic intensity (0.55 INTOP/Byte). Second, we find that the memory footprint of the execution is  $\approx$ 570MB. The total memory traffic generated during runtime is  $\approx$ 267 GB, putting the kernel above the DDR4 peak bandwidth most of the execution time.

GPU platforms. We find that several prior works [201, 124, 35, 42, 53]

propose to accelerate DTW using GPUs. However, these works rely on sharedmemory optimizations that only perform for certain small query sizes. For large query sizes, these implementations either 1) do not work or 2) use high-latency global-memory to hold the main data structures of DTW, which results in large performance penalties. We develop a CUDA-based implementation that supports arbitrary sizes. Then, we analyze DTW using NVIDIA Visual Profiler and observe that its GPU core utilization is below 50% of the theoretical peak performance, and DTW execution is bottlenecked by a large number of accesses to the global memory.

**FPGA platforms**. Several prior works propose [97, 98, 16] to accelerate DTW using FPGAs. However, most of them have very limited onboard memory, and data has to be moved over narrow buses. We develop our own HLS-based FPGA implementation and find that 1) the number of computation units is not enough to exploit the inherent parallelism of DTW, and 2) the compute units spend most of their time waiting for the memory accesses to be served.

**PNM/PUM platforms**. One way of improving parallelism and reducing data movement costs is to perform computation near memory or using the actual memory cells. We analyze several approaches in those directions and detail their benefits and drawbacks:

- General-purpose PNM. This approach typically places small CPU cores in the same die as DRAM. The main benefit of this scheme is that the architecture can be potentially used for general-purpose applications. However, this comes at the cost of limited parallelism. We evaluate a general-purpose PNM (upmem baseline) in 5.3.3, and our evaluations show that this architecture is compute bound when performing the DTW computation.

- <u>Specialized PNM</u>. This approach typically places an ASIC accelerator in the same die as DRAM. The main benefit of this approach is that the processing elements are highly optimized for the target workload. However, the data still needs to be moved from memory to the accelerator. Even though an ASIC accelerator can be used in a PNM architecture, performance would still be bottlenecked by data movement between memory and the accelerator, similarly to general-purpose PNM.

- <u>SRAM-based PUM</u>. This approach uses SRAM-based memory arrays to perform in-situ computation (e.g., compute caches [10]). The main benefits of this approach are the high levels of parallelism and reduced data movement. Unfortunately, SRAM suffers from density and scalability issues [75], along with being radiation vulnerable.

<u>DRAM-based PUM</u>. This approach uses DRAM-based memory arrays to perform in-situ computation (e.g., SIMDRAM [79]). However, this approach involves internal data movement to perform the operations, as data needs to be moved to specific compute-enabled rows before performing the actual operations. Moreover, DRAM suffers from data volatility and destructive read problems.

After identifying which compute paradigm fits better for TSA, the selection of the memory technology is crucial to ensure feasibility of the acceleration solutions. For example, the PNM approach is usually based on DRAM technologies, however high-bandwidth memories (e.g., HBM) are a must to ensure maximum occupancy of the processing elements. When moving to PUM and using the actual cells to perform the computation, it is possible to build accelerators using also DRAM technology, but in this case performance scaling is limited by 1) re-freshing times and specially by 2) the need of moving data to compute enabled rows. Because of that, crossbar-based NVM technologies can overcome those two issues, but it is challenging to support frequent write operations. This is because NVM-based architectures usually suffer from significant latency and energy penalties, and specially low endurance. However, emerging NVM technologies are a possible solution to overcome those drawbacks. We discuss deeper into the memory technology selection on the Background Chapter.

# **1.3.** Thesis Motivation and Contributions

The increasing demand for processing data puts on the table the necessity of providing computing platforms that match the performance requirements. Moreover, energy consumption is a growing critical concern in those platforms. As we show in Section 1.1, TSA is a useful tool to preprocess the immense amount of data that are generated by contemporary devices, thus making the optimization and energy efficiency of TSA as a matter of vital importance. This motivates us to carefully study state-of-the-art TSA algorithms and propose solutions to mitigate their bottlenecks.

In recent times, computer architecture community has identified data movement between memory and processing units as the main bottleneck for scaling up performance. This fact is also applicable to TSA, as we show in Section 1.2. Based on that, platforms that place computation closer to data have been revisited and there are huge research efforts in this direction. We distinguish between Processing-Near-Memory, were compute units are placed physically closer

8

to memory, and Processing-using-Memory, where the actual memory cells are used to perform computation.

The main goal of this thesis is to study if PNM and PUM architectures are good candidates to accelerate TSA and make its computation energy-efficient. Additionally, we study TSA from the algorithmic point of view, reducing the number of floating-point bits required for computation and optimizing resources.

Our main contributions in this thesis and the related publications, which aim to fulfil the goal of it, are the following:

- **PhiTSA** [58]. We optimize and characterize state-of-the-art TSA algorithms in a many-core Intel Xeon Phi KNL platform. We identify data movement as a main bottleneck that 1) prevents from further acceleration and 2) consumes most of the execution energy.

- NATSA [57]. We propose a novel Processing-Near-Memory accelerator for TSA, known as NATSA. This accelerator places custom floating-point processing units close to High-Bandwidth-Memory, exploiting its memory channels and the lower latency of accesses. NATSA significantly improves performance and energy consumption with respect to commodity systems when performing Euclidean Distance based TSA computation.

- MATSA [Under Review]. We propose a novel Processing-Using-Memory accelerator for TSA, known as MATSA. The key idea is to exploit magnetoresistive memory crossbars to enable energy-efficient and fast time series computation in memory while overcoming endurance issues of other nonvolatile memory technologies. MATSA: 1) leverages high levels of parallelism in the memory substrate by exploiting column-wise arithmetic operations, and 2) significantly reduces the data movement costs performing computation using the memory cells. We perform a design space exploration and demonstrate that our HPC version of MATSA greatly improves performance and energy efficiency over server CPU, GPU and PNM.

- **TraTSA** [56, 55]. We evaluate the benefits of applying Transprecision Computing to TSA, where the number of bits dedicated to floating-point operations is reduced. We develop TraTSA, a framework that enables tuning the precision of the operations for every use case, maximizing the resource utilization of the arithmetic units. Using this approach, it is possible to reduce the area required by the system, which enables the possibility of including more arithmetic units thus improve performance and reduce energy consumption.

Additionally, this thesis has contributed to several publications related to the mitigation of the data movement bottlenecks [69, 71, 82, 146, 68, 64].

# 1.4. Thesis Structure

The remainder of this thesis is structured in the following way. In Chapter 2 we provide some background and related work. In Chapter 3 we optimize and characterize a state-of-the-art TSA algorithm in a many-core machine. In Chapter 4 we present NATSA, a novel Processing-Near-Memory accelerator for TSA. In Chapter 5 we present MATSA, a novel Processing-Using-Memory accelerator for TSA. In Chapter 6 we present TraTSA, a framework to optimize the floating-point operations involved in TSA computation. Lastly, Chapter 7 presents the conclusions of this thesis.

# 2 Background and Related Work

In this chapter, we present the some background to support the rest of the thesis. First, we introduce time series analysis and its state-of-the art implementations. Second, we explain the key idea behind Processing Near/In Memory to mitigate the data movement bottleneck. Finally, we provide some insights on how transprecision computing can boost performance and energy efficiency.

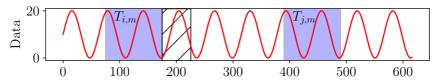

## 2.1. Time Series Analysis

We begin our introduction to time series analysis by providing some basic definitions. A time series T is a sequence of n data points  $t_i$ , where  $1 \le i \le n$ , collected over time. Those data points are usually numeric values that can be represented in any format (e.g., integers or floats). A subsequence of T, also called a *window*, is denoted by  $T_{i,m}$ , where i is the index of the first data point, and m is the number of samples in the subsequence, with  $1 \le i$ , and  $m \le n-i$ . Figure 2.1 shows an example time series with two subsequences highlighted.

Figure 2.1: Example of two subsequences,  $T_{i,m}$  and  $T_{j,m}$ , of a given time series T. Distance  $d_{i,j}$  is calculated from these subsequences. When calculating the matrix profile P, subsequences in the exclusion zone of  $T_{i,m}$  are ignored.

Time series analysis algorithms usually try to find subsequences of interest, like *motifs* (repeated patterns) or *discords* (anomalies). Multiple techniques exist for time series motif and discord discovery [178, 148, 40, 174, 59, 194, 176, 135, 34, 142, 143, 123, 134, 197, 74, 180, 25]. In terms of precision, those approaches can be classified as approximate [179] or exact [196]. Approximate algorithms usually take less execution time than exact ones. However, for large time series, an approximate algorithm can provide inaccurate results as they are based on probabilistic assumptions. Moreover, the user has to set several (even not intuitive) parameters, trying to get results accordingly to the expected ones, a fact which is not always possible. Taking the best of those two approaches, *anytime* algorithms incrementally improve the result over the execution time. This means that if the execution is interrupted before its completeness, a partial solution is obtained. In case the anytime algorithm is executed until the end, the exact solution is obtained. Based on that, we focus our attention on anytime algorithms.

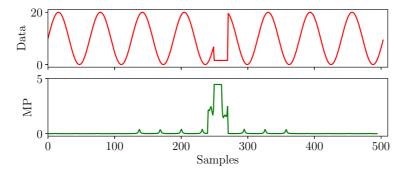

The state-of-the-art exact and anytime set of tools for time series analysis is *matrix profile* [196]. We show a naive example of a matrix profile execution in Figure 2.2, where a sinusoidal time series (red one) presents some anomalies. The output of the algorithm is another time series (the green one, known as *profile*), which contains the distance (similarity) for every subsequence indexed by its first element with respect to the most similar neighbor of the rest of the time series.

Figure 2.2: A time series with some anomalies (discords) and its matrix profile (MP). The anomalies appear as higher distance values in the profile.

The similarity between two subsequences  $T_{i,m}$  and  $T_{j,m}$  can be calculated using the *z*-normalized Euclidean distance, which is defined as follows:

$$d_{i,j} = \sqrt{2m\left(1 - \frac{Q_{i,j} - m\mu_i\mu_j}{m\sigma_i\sigma_j}\right)}$$

(2.1)

where  $Q_{i,j}$  is the dot product of  $T_{i,m}$  and  $T_{j,m}$ ;  $\mu_x$  and  $\sigma_x$  are the mean and the standard deviation of the points in  $T_{x,m}$ , respectively. These statistics are calculated in O(n) time [151], taking negligible time of the whole computation.

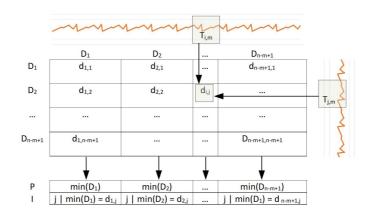

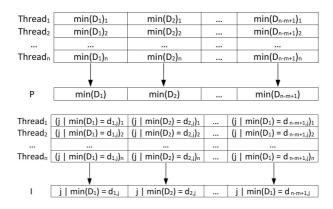

Using the distance in Eq. 2.1 (or another one), the *matrix profile* algorithm solves the similarity search problem in three steps. First, it builds a symmetric  $(n-m+1) \times (n-m+1)$  matrix D, called *distance matrix*. Each cell in D,  $d_{i,i}$ , stores the distance between two subsequences,  $T_{i,m}$  and  $T_{j,m}$ . Second, it creates an array P of size n - m + 1, called *profile*. Each cell  $P_i$  in P keeps the minimum distance recorded in the  $i^{th}$  row of D. Third, it allocates an array I that is of the same size as P, called *profile index*, such that  $I_i = j$  if  $P_i = d_{i,j}$ . This way, P contains the minimum distances between subsequences, while I is the vector of "pointers" to the location of these subsequences within the time series.

Fig. 2.3 depicts an example of the distance matrix D, the profile P, and the profile index I. The neighboring subsequences of  $T_{i,m}$  are highly similar to it (i.e.,  $d_{i,i+1} \approx 0$ ) due to overlapping between them. The algorithm excludes these subsequences from the computation to avoid false positives, by defining an exclusion zone (Figure 2.1) for each subsequence. It follows the approach in [202], where the exclusion zone of  $T_{i,m}$  is  $T_{i,\frac{m}{2}}$  (i.e., ends at  $t_{i+\frac{m}{2}}$  of the time series).

|                    | $\bigwedge \bigwedge $ |                  |                  |                  |  |                                |    | Р                                | Ι                                                                  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|--|--------------------------------|----|----------------------------------|--------------------------------------------------------------------|

| $D_1$              | d <sub>1,1</sub>                                                                                                                                                                                 | d <sub>1,2</sub> | d <sub>1,3</sub> | d <sub>1,4</sub> |  | d <sub>1,n-m+1</sub>           |    | $min(D_1)$                       | j   d <sub>1,j</sub> = P <sub>1</sub>                              |

| $D_2$              | d <sub>2,1</sub>                                                                                                                                                                                 | d <sub>2,2</sub> |                  | d <sub>i,j</sub> |  |                                | -> | min(D <sub>2</sub> )             | j   d <sub>2,j</sub> = P <sub>2</sub>                              |

| $D_3$              | d <sub>3,1</sub>                                                                                                                                                                                 |                  | d <sub>3,3</sub> |                  |  |                                | -> |                                  |                                                                    |

| $D_4$              | d <sub>4,1</sub>                                                                                                                                                                                 |                  |                  | d <sub>4,4</sub> |  |                                | -  |                                  |                                                                    |

|                    |                                                                                                                                                                                                  |                  |                  |                  |  |                                | -> |                                  |                                                                    |

| D <sub>n-m+1</sub> | d <sub>n-m+1,1</sub>                                                                                                                                                                             |                  |                  |                  |  | $d_{\stackrel{n-m+1}{n-m+1'}}$ |    | <i>min</i> (D <sub>n-m+1</sub> ) | $ \begin{array}{c} j \mid d_{n-m+1,j} \\ = P_{n-m+1} \end{array} $ |

Figure 2.3: Example of distance matrix (D), profile (P), and profile index (I).  $P_i$ holds the minimum distance calculated in row  $D_i$ , and  $I_i$  holds the index j of the subsequence that has such distance. Cells in the exclusion zone are coloured red.

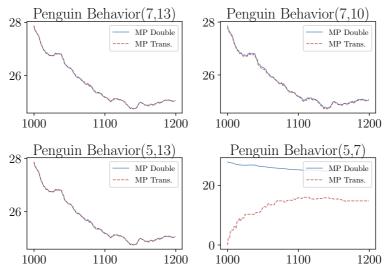

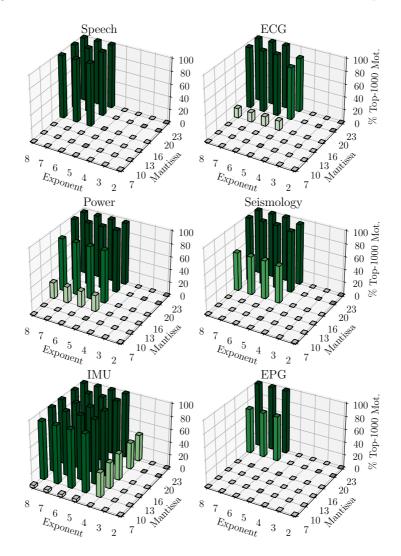

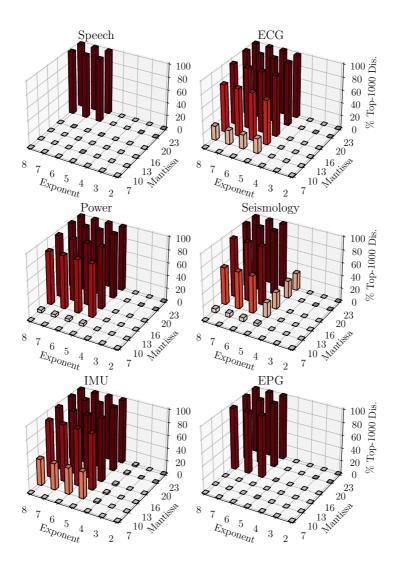

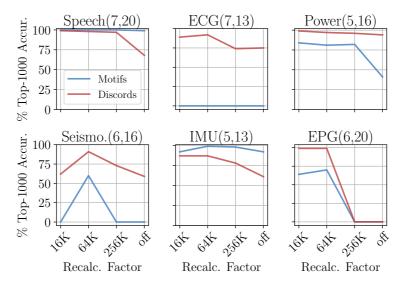

There are several Euclidean-Distance-based implementations of matrix profile, including STAMP [196], STOMP [86], SCRIMP [202] and SCAMP [203]. SCRIMP is the state-of-the-art CPU-based implementation. Prior acceleration approaches to time series analysis [86, 202] mainly focus on accelerating STOMP