# STUDY OF FINFET TRANSISTOR: CRITICAL AND LITERATURE REVIEW IN FINFET TRANSISTOR IN THE ACTIVE FILTER

# **Arsen Ahmed Mohammede**

Engineering Faculty, Electrical Department, Kirkuk, Iraq arsenahmed@uokirkuk.edu.iq

#### Zaidoon Khalaf Mahmood

University of Kirkuk, Iraq

# Doç.Dr. Hüseyin Demirel

Engineering Faculty, Electrical Department, Karabuk, Turkiye

**Reception**: 28/10/2022 **Acceptance**: 25/12/2022 **Publication**: 18/02/2023

#### Suggested citation:

A.M., Arsen, K.M., Zaidoon and D. Hüseyin. (2023). **Study of finfet transistor:** critical and literature review in finfet transistor in the active filter. *3C TIC. Cuadernos de desarrollo aplicados a las TIC, 12(1),* 65-81. <a href="https://doi.org/10.17993/3ctic.2023.121.65-81">https://doi.org/10.17993/3ctic.2023.121.65-81</a>

## **ABSTRACT**

For several decades, the development of metal-oxide-semiconductor field-effect transistors have made available to us better circuit time and efficiency per function with each successive generation of CMOS technology. However, basic product and manufacturing technology limitations will make continuing transistor scaling difficult in the sub-32 nm zone. Field impact transistors with fins were developed. offered as a viable solution to the scalability difficulties. Fin field effect transistors can be made in the same way as regular CMOS transistors, allowing for a quick transition to production. The use of inserted-oxide FinFET technology was presented as a solution to continue transistor scaling. Due to gate fringing electric fields through the added oxide (SiO2) layers, the electromagnetic integrity of an iFinFET is superior to that of a FinFET. We discovered that the proposed mobility model functions admirably and that the Joule effect mostly influences the drain current and the heat source. The major goal of this work is to compare the performance characteristics of combinational logic using CMOS and FinFET technology. The inverting gate is modelled in HSPICE simulation on a 32nm transistor size utilising CMOS and FinFET structures, and respective performances, such as energy consumed, are examined.

#### **KEYWORDS**

Approximation electronic conductivity, Metal-oxide-semiconductor field-effect transistors, Network for energy conversion, FinFET, Adder, Energy utilization, Simulation

# **PAPER INDEX**

**ABSTRACT**

**KEYWORDS**

- 1. INTRODUCTION

- 2. WIRE SURVEY CIRCUITS

- 3. FINFET TECHNOLOGY

- 4. FINFET HAS UPSIDES OVER CLASSIC MATERIAL PADDOCK TRANSFORMER

- 4.1. FINFETS CIRCUITS USED BY RESEARCHERS

- 5. INVESTIGATORS' MOSFETS DEVICES, METRICS, AND FACTS

- 6. OUTPUT WITH COMPUTATION

- 6.1. FINFET BASED INVERTER

- 7. CONCLUSION

REFERENCES

## 1. INTRODUCTION

Larger quantities FinFET innovation is being employed for high-volume production of CMOS microchips in the sub-20 nm generation [1, 2]. A p-channel FinFET's output efficiency of the same fin height is exactly comparable even to an n-channel FinFET with same element size due to the 110 winglet crystalline phase and a higher level of deformation stimulated in the channel region by ingrained sio2 source/drain regions [1]. Though that is advantageous for applications that demand logic circuits, it reduces the write ability of a statically six mosfet recording cell with two individuals Mosfet carry FinFETs, and two lift FinFETs [3]. The insertion-oxide FinFET (iFinFET) technology has been presented as a solution to continue transistor scaling [4]. The atomic fidelity of an iFinFET is higher than that of a FinFET due additional gate surrounding electric fields created by the additional oxide sheets. The door field-effect semiconductor delivers improved electric purity at the cost of a greater intrinsic delay [4]. According to a slew of recent studies, triple gate (DG) gadgets are the best option. In comparison to planar double gate semiconductors, quasi-planar FinFET is the easiest to fabricate among the numerous types of DG devices.

Fin field effect transistors use an extremely thin undoped body to reduce SCEs by suppressing subsurface leakage channels. An undoped or lightly doped [6] body decreases Vt changes caused by Irregular dopant oscillations promote carrier concentration and lead to a higher on current.

The capacity of the gateway gate to control the prediction capability and current will flow in the inversion layer decreases as devices shrink in size, and undesired characteristics known as "relatively brief effects" begin frequently plague iron field-effect semiconductors. Scaling typical "bulk" titanium field-effect devices below 20nm looks to be impossible for a variety of reasons [5]. If the limitation could not be removed, Allen's law would come to end around a year.

The Voltage-Doping Transformation model is a basic tool that may reasonably be expected to convert the impacts of incorporating system variables including barrier height and depletion power [6,7] into design parameters. The following formulas can be generated from the concept in the case of the narrow effect and waste barrier reducing:

$$I_{D\cong I_{DSS}} \left[ 1 - \frac{V_{GS}}{V_{GS(Off)}} \right]^2$$

where  $V_{GS}$  is the high voltage size of connexion with the built-in possibilities of the possible cause or drain, tox is the multi gate texture, is really the discharge and origin crossroad complexity, and tdep is the gate field absorption depth in the inversion layer, which is equitable to the complexity of the depletion region beneath the gate in noble metal field-effect transistors. The "Electrodynamic Integrity" factor is the name of the parameter. It's a measurement of how and why the draining's lines of force effect the stream zone [8], creating the relatively brief effect and fluid barrier lowering effects. It is dependent on the device design. The resistance value of an iron field-

effect diode with a particular gate length let can be computed by applying formulas based on the previous formulae.

$$I_D \cong I_{DSS} \left[ 1 - \frac{V_{GS}}{V_{GS(\text{ off })}} \right]^2 = 40 \ mA \left[ 1 - \frac{-2}{-6} \right]^2$$

where is the relationship? A lengthy device's duty ratio is V GS. The "duty cycle roll-off" The drain current lowers as the size of the device falls, but it is a well relatively brief phenomenon. As indicated in any of these calculations, the overall impacts can be decreased by reducing the circuit length the multi - gate thicknesses. Symptoms can also be lowered by raising the intensity of doping and minimizing the depletion depth. However, due to the increased tunneling current associated with decreasing valve thicknesses, gate oxides can really be scaled beyond a certain point. Lower the depletion depth just under the [9] to the substrate as another method of mitigating short-channel effects. Shorter depletion zones and, as a result, lower parasitic capacitances are associated with a narrower depletion width. As a result, the leakage regime's sub-threshold slope improves. Reduced depletion width, on the other hand, correlates to reduced barrier impact on the canal, leading in a longer downstream section change on/off. When the gate's Electromagnetic wires from the emitter and collector effect channel area adjustment, short-channel effects occur.

Figure 1 depicts these field lines. In a macroscopic device, local equipotential lines flow over the depleting zone coupled with the contacts (Fig. 1). Their effects on the circuit can be reduced by increasing the sorption capacity in the inversion layer. Regrettably, in very embedded systems (1106 cm-3) the pl intensity is now too strong for efficient transient conditions.

Figure 1. Metal-oxide-semiconductor paddock devices with two gates.

The Electro - static Ethics quotient of a bulk devices can be calculated using the Battery New methodology, which can really be described thus:

$$I_D \cong I_{DSS} \left[ 1 - \frac{V_{GS}}{V_{GS(\text{ ff })}} \right]^2 = 40 \ mA \left[ 1 - \frac{-5}{-6} \right]^2$$

Both valves of a double-gate mechanism are linked together. The electrical charge traces from the app's gate and source cease on the bottom positive terminal [10,11], preventing them from reaching the channel region Fig. 1. The only boundary layers that can encroach on the inversion layer and damage short-channel features are those that propagate through the si substrate itself [30]. The thickness of the silicon sheet can be lowered to decrease encroachment. The developing and developed field plus optimal circuit depths depth with each gate in a double-gate device are both equal to tSi/2.

The Electrochemical Stability factor of that double device can be calculated using the Voltage-Doping Modeling approach, which can be expressed as

$$I_D = I_{DSS} \left[ 1 - \frac{-V_{GS}}{-V_{GS(Off)}} \right]^2$$

The facts in formula 1.8 leads to an essential conclusion: bulk semiconductors then when you've ran, they reach a maximum extent when they run out of energy. of 25-30 nm, while double arrangement is the only way to attain that all lengths.

Section 1 offered an overview of silver paddock circuits and FinFET [12-15] devices in Sections 2 and 3. FinFET's advantages over metal field-effect semiconductors and FinFET circuits are explored in Section 4. Important investigations and facts were reported in sections 5. Parameters and results used by investigators and the modeling results are reported in section 6. In Section 7 the conclusion of paper is given.

#### 2. WIRE SURVEY CIRCUITS

Aside from Bipolar Junction Transistor, Metal-Oxide Semiconductor Field-Effect Transistors, or simply metal-oxide-semiconductor field-effect transistors [16], are another form of transistor (BJT). In 1960, Kahng and Atalla invented the very first metal-oxide-semiconductor field-effect transistors [17], which are more cost-effective than BJT a single crystal silicon chip with a huge transistor count Field-effect devices made on electrode materials have four terminals in the level of cash running seen among collector and emitter is determined by the power delivered to the inverting input. This semiconductor can be thought of as a switch to some extent. As between evaporator and the condenser, a conduction trench forms when the gate voltage applied is larger than the threshold voltage, electricity flows seen between two terminals [18-20].

If the gate voltage is less than the threshold voltage as shown in Fig. 2, no conducting channel will form, and the transistor will be deemed an open circuits. When strong reversal develops, the input impedance, The turnstile power is regulated in Vout.

Wire field-effect transistor come in a range of sizes. The n-type outflow, n-type supplier, and p-type framework make up an n-channel MOS or NMOS transistor.

Figure 2. Brass ground diodes with N layers

PMOS, or p-channel, is another type of industrial practice area transistor with a c h base, p-type drains, and p-type sources.

Figure 3. Brass ground diodes with P layers

Because both diodes are employed in a circuit, it is now referred to as Composite. Furthermore, as previously stated, each type of transistor can be categorized into two types: enrichment and degradation modes. Under the corrosion products that connects the drain and source in an enhancement mode transistor as in Fig 3, there is no channel. The source to drain wires would only be coupled [21-24] when a strong voltage was applied, forming of an e drift region behind corrosion products. The channel in a depletion mode transistor is readily available beneath the oxide layer. An electron result of adding or a doped impurity can serve as the channel. The presence of a channel allows the drain and source wires to be connected directly.

#### 3. FINFET TECHNOLOGY

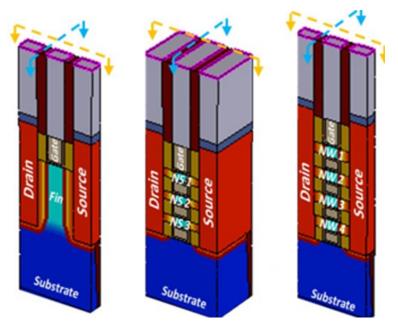

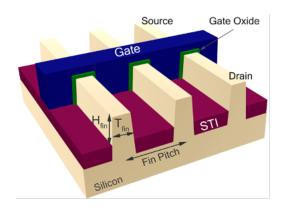

FinFET is an of pas' circuit with a "fin-like" form, the semiconductor channel is formed by the gated wrapping about over the fin. It's also characterized as a quasilinear route since the electricity passes transverse to the diamond surfaces and the channel is diagonal to the substrate line.

Figure 4. FinFET's Configuration

All of the devices in this paper were created using the Schematic capture Simulation Finite element analysis suite, which allows nano-scale mosfets to be appropriately modelled using particle corrected glide transport schema, rising 2D meshes, Vibrational energy facts, barrier tunneling modelling using the Hartree approximate solution, and peripheral cues mobility's [25]. As a result, the outcome of the analysis study combines two main subatomic particles consequences.

In a Fet, a conducts cell is formed by a super Si fin device, allowing electrons to flow from source to drain. The inputs come from a gate that arcs around the function held. As a result, even when the circuit is turned off, regulating electron flow avoids current leakage. The volume of charged particles and indeed the velocity at which these runs can sometimes increase, leading a single fin's secondary flow to break. This stops the electric current by interrupting the electron flow from the inlet to the outlet. The partial volume effect is enhanced by paddock semiconductors with many gates that have been built in line with each other. The quantity of fins controls the quantity of charged particles flowing from greater potential to reduced prospective. As a result, as the rate with which the particles flow is faster, the switch velocity is high. The main advantage of many fins is that they provide better switching speed over the conduction channel. Fig 4 shows a response; energy leaking is decreased. This produces a large quantity with on

operational voltage. Fin magnetic coil transistors are available in many different logic architectures. The amplifier can be constructed in the one of the following ways, dependent on the fin optoelectronic devices used:

- Impedance phase: In this method, both gates are shortened, resulting in greater drive force and best channel duration control.

- The impartial mode, wherein the on those gates are driven by different signals, may lower the quantity of semiconductors in the circuit.

- Reduced mode, where another the n-type is exposed to a voltage level. FinFETs

while a voltage applied to p-type FinFETs. This changes the phone's input

impedance, reducing leaky leakage power at the cost of increased latency.

# 4. FINFET HAS UPSIDES OVER CLASSIC MATERIAL PADDOCK TRANSFORMER

Following are the main advantages of Supervision over the channel is improved shown in Table 1:

- · Narrow effects have been suppressed.

- Dynamic leakage current is reduced.

- Shifting speed is increased.

- Increased drain potential (More drive-current per footprint)

- Reduce the switching energy.

- Power usage is low.

**Table 1.** Advantages of FinFET over Traditional metal-oxide-semiconductor field-effect transistors

|           | Portal FET        |                  | Photovoltaic of Passivation Layer FET |                    |     |     |

|-----------|-------------------|------------------|---------------------------------------|--------------------|-----|-----|

| Category  | Exhaustion Method | Shrinking Method |                                       | Improvement Method |     |     |

| N-channel | OV                | OFF              | ON                                    | OFF                | ON  | OFF |

| P-channel | OV                | +ve              | OV                                    | +ve                | -ve | oV  |

#### 4.1. FINFETS CIRCUITS USED BY RESEARCHERS

Chen et. al. [7] suggested a Nano-scale FinFET circuit sturdiness (reliability and scalability) analysis. One of the most difficult challenges for nanoscale VLSI designers is ensuring dependability. Circuit dependability is negatively impacted by smaller shapes, low output supply, and higher frequencies: these characteristics increase the incidence of soft errors, and larger degrees of device parameter variation transform the design challenge from predictable to probability. As a corollary, reducing fault rates and reducing variance influence has become extremely critical. The Transistors circuit was introduced as a beautiful dual FET version that enables for innovation growth in the future. [26] demonstrated that FinFET logic can be implemented at 160nm for the first time by demonstrating inverter-chain functionality. Joshi et al analyzed the behavior of FinFET SRAM and found that it has superior performance and lower power than standard planar PD-SOI. IBM was the first company to successfully convert an existing microprocessor design to 100 nm FinFET technology. [9] proved that an Inverter SRAM architecture had a 30% good disturbance margin than a traditional SRAM system than a bulk CMOS SRAM. The HSPICE tool from Synopsys is used to examine FinFET behavior. FinFET circuits are compared to include massive networks 21nm and 34nm technology in the studies. Over Bulk CMOS designs, FinFET-based designs reduce delay variation by an average of 83 percent and 43

percent for logic gates and memory cells, respectively. The findings suggest that FinFET circuits have superior reliability and scalability, as improved fault immunity and far less quality assured from process parameters are indications of this.. FinFETbased circuit design is found to be more robust than bulk CMOS-based circuit design [27]. With the upcoming FinFET technology, assessed a series of innovative memory circuit approaches. Storage durability, leaky energy usage, and cell area for individual FinFET Dynamic ram, cross level, and low-quality tied-gate In a 24angstrom FinFET innovation, Mosfets Memory cells were studied. When compared to the smaller quality paired gate FinFET dynamic ram seen in 41nm FinFET technology, the reading safety of the specifically relates dynamic unbiased FinFET SRAM cells improves by up to 92 percent. The task constructed multi-Vt FinFET SRAM cells reduce idle mode power losses and cell surface by up to 45X and 15.5 percent, however, when relative to a typical low cutoff bound FinFET SRAM cell scaled for equivalent read stability. [28] investigated the statistical reliability and power losses of FinFET SRAM cells with dynamic vth tuning in the presence of process parameter variations. When the channel length of a single gate metal-oxide-semiconductor field-effect transistor is shortened and cascading improves quality by increasing impedance and gain while lowering series resistive loss. After executing the sequence to serial translation of the analogous circuit, cascading aids in the correction of given series, both lead to the concurrent resistive loss.

At the very least, the cascade device's overdrive voltage limits the output swing. In a cascade construction, the minimal power supply required is 4Vsat, which is met in this design. The enhanced quality of the cascade arrangement causes the terminal voltage range limitation. The optimal current sources are replaced by device. The Al's total serial resistive loss is controlled by VB. Variables in the Al's self-reflecting resonance can also be used to manipulate it. As a result, the proposed technique is the best fit for the situation.

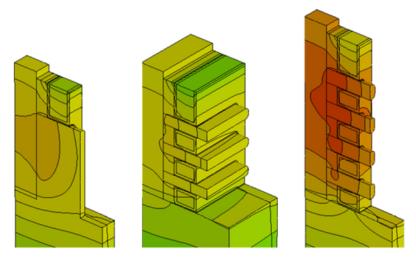

We have really been able to prove basic gates and logic units based on such relatively basic yet foundational optimization of Cws levels via WFE, as addressed in our latest studies [29]. These static CMOS gates, as well as their logic features obtained by TCAD calculations, are briefly revisited in Fig.4. They show that designing absolutely lowest logic circuits in terms of device counts and area is doable by giving a maximum of two or three labor in the Super bowl and gate metals of FinFETs. These benefits translate to decreased energy consumption and 2 - 3 decades in these new gates, resulting in PDP statistics that are comparable to their typical FinFET counterparts, but being slower in switching due to the standalone gate configuration's lower electrical characteristics.

The researchers examined blended design as double FinFET technology using a voltammetric regulator oscillators as a research study. Due to increased Short-Channel Effects, using standard planar single gate metal-oxide-semiconductor field-effect transistors is becoming increasingly challenging (SCEs). Random dopant fluctuations (RDF) in the channel region of planar metal-oxide-semiconductor field-effect transistors, in addition to SCEs, are regarded to be the primary cause of baseline voltage variations between devices made on another wafer. The authors

introduce FinFETS technology, which reduces variability owing to Stochastic dopant variations thanks to a doped samples or weakly treated material and reduces carrier motion depreciation. Due to Sub - threshold fluctuations, the FinFET Controller has a 3.93 percent variability, but the Cmp VCO has 17.98 percentage variance, indicating that fin field effect transistors are so much more process time tolerant. The following are some of FinFET's key benefits: (1) Almost perfect sub-threshold slope (2) Inherent gate capacitance is low. (3) Junction capacitances that are smaller. (4) Increased resistance to SCEs. (5) A higher ratio of (ION/IOFF). (6)Shorted gate (SG) and independent gate (IG) choices provide circuit design freedom. Thermal issues will be investigated in future study, as fin field effect transistors suffer from self-heating[12]. [25] outlines an effort to investigate (1) A comparison of FinFET devices is viewed for analog signals schematic capture; (2) Output strain, impedance, Transparent gain, but instead transition rate are examined Gd FinFET operating including both significant invert and reduced load zones; (3) Statistical spatially varying evaluation for all the above FinFET specifications in both large and powerful distortion and low current regions of DG FinFET activity Vth fluctuation, small channel implications and manufacturing variances plague nanoscale bulk CMOS technology. FinFET technology is utilized to improve SCE and process variation immunity. If both selecting bits go low in the end state, the circuit presented in previous section gate can easily be adjusted to construct an Opcode function. While one of the pull-down mosfet connections is changed from S0 to S1, the circuit discharge its output anytime the inputs (A&B) go low, as shown in Fig.5. This only affects the situation where both select indicators are low, resulting in the Operands procedure in the last event. The two 4T circuits shown above show how the WFE may neatly effect the same network with modest input changes, boosting its performance and adding to the sequence set. Applying MTCMOS and SVL Leakage Reduction Technique, [30] designed and constructed a FinFET Based Inverter. Because of a substantial impact on a dedicated channel, which results in an actual growth in short channel effects and heightened attention to processing alterations, scaling of standard single-gate bulk metal-oxidesemiconductor field-effect transistors faces great hurdles in the nanoscale regime. When compared to standard CMOS, double-gate FinFETs have better SCEs performance [26,27,28], which encourages upgrading of tech. The article compares hang leaks, delay, and overall power usage of the logic gate in different settings of FinFET innovation. Simulations are carried out at 35angstroms using the Tcad tool. MTCMOS and Inefficiencies pragmatic circuit-level technologies are used to create a layout with provides speed and low power consumption and maximum volt devices. The fin field effect transistors based inverter using SVL approach has a 50-60% lower leakage power than a typical FinFETs based inverter and a 25-30% lower leakage power than a fin field effect transistors based inverter using MTCMOS technique, according to simulation results. Fin field effect transistors based inverters using the MTCMOS technology use 65-70 percent less power than standard inverters and 35-40 percent less power than fin field effect transistors based inverters using the SVL technique. The SVL technique is superior than the MTCMOS technique for minimizing leakage power and delay, however the SVL technique consumes more power than the MTCMOS technique. This solution technique is found to be the greatest fit for the given problem [31].

# 5. INVESTIGATORS' MOSFETS DEVICES, METRICS, AND FACTS

In the meantime, each fin has its own breadth, thickness, and structure. Coating, etching, and other processes are used to create the fins. The gate, of naturally, has a number of properties, one of which is the turnstile length.

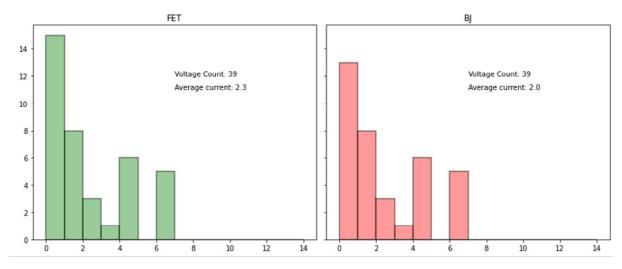

The foundation goes through numerous lithography processes, including provides a soft patterning, in one FinFET supply chain. The base is patterned with spacer-like features in this method. An etcher then carves vertical tunnels down into the floor between these structures, generating fins. The spaces are then replaced with oxide to use an epitaxial growth. After polishing the top section, the device is subjected to a recess etch stage. After that, a gate dioxide is applied, followed by the barrier development. Table 2 illustrates about devices, metric's and important facts. It is also clear from Fig. 5 that BJ is affected more in comparison to FET.

Table 2. Investigators' Mosfets Devices, Metrics, and Facts

|    | Field Effect Transistor (FET)          | Bipolar Junction Transistor (BJ)     |  |  |

|----|----------------------------------------|--------------------------------------|--|--|

| 1  | Intensity at voltage level             | Intensity at high frequency          |  |  |

| 2  | Significant current gain               | Less current gain                    |  |  |

| 3  | Highly Insertion loss                  | Less Insertion loss                  |  |  |

| 4  | Resistive output                       | Medium noise generation              |  |  |

| 5  | Reduced noise generation               | High noise generation                |  |  |

| 6  | Fast switching time                    | Medium switching time                |  |  |

| 7  | Electrical disruption is common        | Robust                               |  |  |

| 8  | Some require an input to turn it "OFF" | Requires zero input to turn it "OFF" |  |  |

| 9  | Voltage controlled device              | Current controlled device            |  |  |

| 10 | Exhibits the properties of a Resistor  | Cheap                                |  |  |

| 11 | More expensive than bipolar            | Easy to bias                         |  |  |

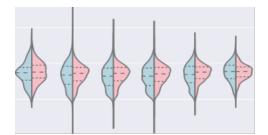

**Figure 5.** Comparison between FET and BJ on the basis of voltage count and average current

# 6. OUTPUT WITH COMPUTATION

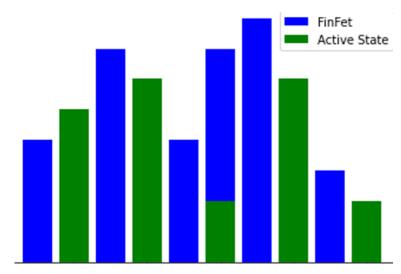

In this part, we show simulated results for a 32nm FinFET-based converter and a 32nm wire field-effect transistor-based converter, as well as average output calculations for rectifier gates in various modes using HSPICE. Table 3 provides the parameters of FinFET and material field-effect devices that were employed in the Matlab simulation inverters simulation.

Table 3. Parameters used in Experimentation

| NPN     | PNP     | $V_{CE}$ | $I_{C(max)}$ | $P_d$  |

|---------|---------|----------|--------------|--------|

| BC547   | BC557   | 45v      | 100 mA       | 600 mW |

| BC447   | BC448   | 80v      | 300 mA       | 625 mW |

| 2 N3904 | 2 N3906 | 40v      | 200 mA       | 625 mW |

| 2 N2222 | 2 N2907 | 30v      | 800 mA       | 800 mW |

| BC140   | BC160   | 40v      | 1.0 A        | 800 mW |

| TIP29   | TIP30   | 100v     | 1.0 A        | 3 W    |

| BD137   | BD138   | 60v      | 1.5 A        | 1.25 W |

| TIP3055 | TIP2955 | 60v      | 15 A         | 90 W   |

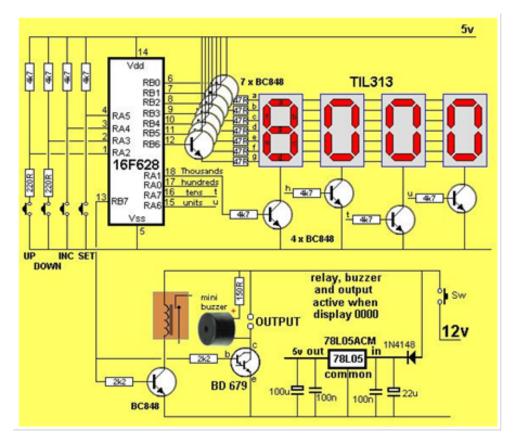

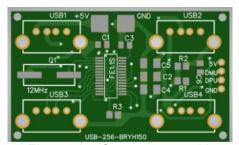

Figure 6. Steel field-effect devices are used in this bridge rectifier

**Figure 7.** Found Using the following on Discharge Investigation in Metal-Oxide VIsi Field-Effect Silicon chips

Figures 6 and 7 illustrate the circuit diagram and feedback characteristics of the inverter metal - oxide field-effect transistors. For the test, the supply voltages used were 0.6V for 52nm technologies. A pulse is often used to represent input input.

#### **6.1. FINFET BASED INVERTER**

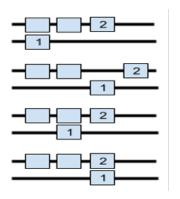

Fig8, Fig9, Fig10, and Fig11 illustrate the circuit of an accelerator using FinFET architecture in the Quick (SG) mode, Reduced (LP) mode, Unbiased (IG) mode, and

Composite mode (IG/LP) modes, accordingly. H-SPICE simulation was performed them in a 32-nm technology node. The inputs are applied to the inverter, they are propagated via the converter, and indeed the insight parameters of FinFET based reactors are presented in Fig12.

**Figure 8.** Amplifier Loop in Quick Mode

**Figure 9.** Separator Component Reduced Mode applyting FinFET Technology

Figure 10. Concentrator with Unbiased Mode

**Figure 11.** Splitter Component in LP Configuration Circuit applyting FinFET

Table 4. Total Energy Comparison

| S. No | Technology | Methodology          | Average Power   |

|-------|------------|----------------------|-----------------|

| 1     | 42nm       | Massive Radial MOSFT | 2.4813E-04 watt |

| 2     | 42nm       | FinFET(SG Mode)      | 3.3988E-05 watt |

| 3     | 42nm       | FinFET(LP Mode)      | 7.1432E-05 watt |

| 4     | 42nm       | FinFET(IG Mode)      | 2.4868E-04 watt |

| 5     | 42nm       | FinFET(IG/LP Mode)   | 2.2091E-04 watt |

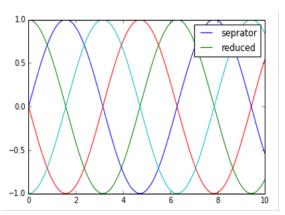

Figure 12. Pg, Lh, Gs, & Unmutated FinFET Converter Discharge Investigation

#### 7. CONCLUSION

To brief, we constructed Au-gated pan FETs as well as Fin-FETs with variable fin-widths using Tio2 composite thin films including extreme density 2DEGs. We discover a mathematical gate impedance reduction in the constructed FinFETs when compared to planar FETs. We show that scaling down the Tio2 fin widths improves gate capacitance even further. We were able to increase the discharge capacity in the Mosfets with the shortest fin-widths when comparing to the produced planar FETs, resulting in a new dopant electron concentrations modulation. We expect that by narrowing the fin-widths even more, we will be able to modulate the 12 electron per unit cell 2DEG density completely. We believe that employing the FinFET technique to improve massive carrier content modulation in complicated oxides would eventually lead to reversible control of emerging phenomena in these materials. Using HSPICE, this research measured the effectiveness of an inverter generator to that of traditional silicon inverters brass field-effect transistors. The overall power consumption of the FinFET circuit is substantially lower than that of the planar iron field-effect passive components circuit.

#### REFERENCES

- (1) Kuhn, K. J. (2011, April). CMOS scaling for the 22nm node and beyond: Device physics and technology. In Proceedings of 2011 International Symposium on VLSI Technology, Systems and Applications (pp. 1-2). IEEE.

- (2) Roy, K., Mukhopadhyay, S., & Mahmoodi-Meimand, H. (2003). Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. *Proceedings of the IEEE*, 91(2), 305-327.

- (3) Frank, D. J., Dennard, R. H., Nowak, E., Solomon, P. M., Taur, Y., & Wong, H. S. P. (2001). **Device scaling limits of Si MOSFETs and their application dependencies**. *Proceedings of the IEEE*, 89(3), 259-288.

- (4) Hu, C. (1996). **Gate oxide scaling limits and projection**. In *International Electron Devices Meeting. Technical Digest* (pp. 319-322). IEEE.

- (5) Yeo, Y. C., King, T. J., & Hu, C. (2003). **MOSFET gate leakage modeling and selection guide for alternative gate dielectrics based on leakage considerations**. *IEEE Transactions on Electron Devices*, 50(4), 1027-1035.

- (6) Chen, J., Chan, T. Y., Chen, I. C., Ko, P. K., & Hu, C. (1987). Subbreakdown drain leakage current in MOSFET. IEEE Electron Device Letters, 8(11), 515-517.

- (7) Bandung, S. T. T., STT Bina Tunggal, and STT Dr Khez Muttaqien. (2013). International technology roadmap for semiconductors. <a href="http://www.itrs.net">http://www.itrs.net</a>.

- (8) Skotnicki, T., Hutchby, J. A., King, T. J., Wong, H. S., & Boeuf, F. (2005). The end of CMOS scaling: toward the introduction of new materials and structural changes to improve MOSFET performance. *IEEE Circuits and Devices Magazine*, 21(1), 16-26.

- (9) Wong, H. S., Frank, D. J., & Solomon, P. M. (1998, December). Device design considerations for double-gate, ground-plane, and single-gated ultra-thin SOI MOSFET's at the 25 nm channel length generation. In *International Electron Devices Meeting 1998. Technical Digest (Cat. No. 98CH36217)* (pp. 407-410). IEEE.

- (10) Solomon, P. M., Guarini, K. W., Zhang, Y., Chan, K., Jones, E. C., Cohen, G. M., ... & Wong, H. S. (2003). Two gates are better than one [double-gate MOSFET process]. *IEEE circuits and devices magazine*, 19(1), 48-62.

- (11) Suzuki, K., Tanaka, T., Tosaka, Y., Horie, H., & Arimoto, Y. (1993). **Scaling theory for double-gate SOI MOSFET's**. *IEEE Transactions on Electron Devices*, 40(12), 2326-2329.

- (12) Nowak, E. J., Aller, I., Ludwig, T., Kim, K., Joshi, R. V., Chuang, C. T., ... & Puri, R. (2004). **Turning silicon on its edge [double gate CMOS/FinFET technology]**. *IEEE Circuits and Devices Magazine*, 20(1), 20-31.

- (13) Yan, R. H., Ourmazd, A., & Lee, K. F. (1992). Scaling the Si MOSFET: From bulk to SOI to bulk. *IEEE Transactions on Electron Devices*, 39(7), 1704-1710.

- (14) Choi, Y. K., Asano, K., Lindert, N., Subramanian, V., King, T. J., Bokor, J., & Hu, C. (1999, December). **Ultra-thin body SOI MOSFET for deep-sub-tenth micron era. In International Electron Devices Meeting 1999**. *Technical Digest* (Cat. No. 99CH36318) (pp. 919-921). IEEE.

- (15) Doris, B., Cheng, K., Khakifirooz, A., Liu, Q., & Vinet, M. (2013, April). Device design considerations for next generation CMOS technology: Planar FDSOI and FinFET. In 2013 International Symposium on VLSI Technology, Systems and Application (VLSI-TSA) (pp. 1-2). IEEE.

- (16) Kong, B. S., Kim, S. S., & Jun, Y. H. (2001). **Conditional-capture flip-flop for statistical power reduction**. *IEEE Journal of Solid-State Circuits*, 36(8), 1263-1271.

- (17) Liu, B., & Wang, B. (2015). **Reconfiguration-based VLSI design for security**. *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, 5(1), 98-108.

- (18) Piguet, C. (2004). Low-Power Electronics Design, Solid-State Circuits, New York

- (19) Ghai, D., Mohanty, S. P., & Thakral, G. (2013, August). Comparative analysis of double gate FinFET configurations for analog circuit design. In 2013

- IEEE 56th International Midwest Symposium on Circuits and Systems (MWSCAS) (pp. 809-812). IEEE.

- (20) Ghai, D., Mohanty, S. P., & Thakral, G. (2013, August). **Double gate FinFET based mixed-signal design: A VCO case study**. In 2013 IEEE 56th International Midwest Symposium on Circuits and Systems (MWSCAS) (pp. 177-180). IEEE.

- (21) Wang, F., Xie, Y., Bernstein, K., & Luo, Y. (2006, March). **Dependability** analysis of nano-scale FinFET circuits. In *IEEE Computer Society Annual Symposium on Emerging VLSI Technologies and Architectures (ISVLSI'06)* (pp. 6-pp). IEEE.

- (22) Partovi, H., Burd, R., Salim, U., Weber, F., DiGregorio, L., & Draper, D. (1996, February). Flow-through latch and edge-triggered flip-flop hybrid elements. In 1996 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, ISSCC (pp. 138-139). IEEE.

- (23) Mahmoodi-Meimand, H., & Roy, K. (2004, May). **Data-retention flip-flops for power-down applications**. In 2004 IEEE International Symposium on Circuits and Systems (IEEE Cat. No. 04CH37512) (Vol. 2, pp. II-677). IEEE.

- (24) Halter, J. P., & Najm, F. N. (1997, May). A gate-level leakage power reduction method for ultra-low-power CMOS circuits. In *Proceedings of CICC 97-Custom Integrated Circuits Conference* (pp. 475-478). IEEE.

- (25) Tschanz, J., Narendra, S., Chen, Z., Borkar, S., Sachdev, M., & De, V. (2001, August). Comparative delay and energy of single edge-triggered & dual edge-triggered pulsed flip-flops for high-performance microprocessors. In *Proceedings of the 2001 international symposium on Low power electronics and design* (pp. 147-152).

- (26) Moon, J. S., Athas, W. C., Beerel, P. A., & Draper, J. T. (2002, May). Low-power sequential access memory design. In *Proceedings of the IEEE 2002 Custom Integrated Circuits Conference (Cat. No. 02CH37285)* (pp. 111-114). IEEE.

- (27) Rabaey, J. M., Chandrakasan, A. P., & Nikolic, B. (2002). **Digital integrated circuits (Vol. 2)**. *Englewood Cliffs: Prentice hall.*

- (28) Hu, J., & Ye, L. (2010, August). P-type complementary pass-transistor adiabatic logic circuits for active leakage reduction. In 2010 Second Pacific-Asia Conference on Circuits, Communications and System (Vol. 1, pp. 94-97). IEEE.

- (29) Cao, K. M., Lee, W. C., Liu, W., Jin, X., Su, P., Fung, S. K. H., ... & Hu, C. (2000, December). **BSIM4 gate leakage model including source-drain partition**. *In International Electron Devices Meeting 2000. Technical Digest. IEDM (Cat. No. 00CH37138)* (pp. 815-818). IEEE.

- (30) Benini, L., De Micheli, G., & Macii, E. (2001). **Designing low-power circuits:** practical recipes. *IEEE Circuits and Systems magazine*, 1(1), 6-25.

- (31) Su, L., Zhang, W., Ye, L., Shi, X., & Hu, J. (2010, January). An Investigation for Leakage Reduction of Dual Transmission Gate Adiabatic Logic Circuits with Power-Gating Schemes in Scaled CMOS Processes. In 2010 International Conference on Innovative Computing and Communication and 2010 Asia-Pacific Conference on Information Technology and Ocean Engineering (pp. 290-293). IEEE.